Advance Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1

Copyright

©

Cirrus Logic, Inc. 2004

(All Rights Reserved)

Cirrus Logic, Inc.

www.cirrus.com

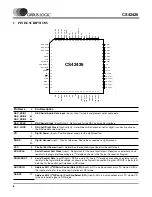

CS42426

114 dB, 192 kHz 6-Ch Codec with PLL

Features

Six 24-bit D/A, two 24-bit A/D converters

114 dB DAC / 114 dB ADC dynamic range

-100 dB THD+N

System sampling rates up to 192 kHz

Integrated low-jitter PLL for increased system

jitter tolerance

PLL clock or OMCK system clock selection

7 configurable general purpose outputs

ADC high pass filter for DC offset calibration

Expandable ADC channels and one-line

mode support

Digital output volume control with soft ramp

D/-15 dB input gain adjust for ADC

Differential analog architecture

Supports logic levels between 5 V and 1.8 V

General Description

The CS42426 CODEC provides two analog-to-digital and six

digital-to-analog Delta-Sigma converters, as well as an inte-

grated PLL, in a 64-pin LQFP package.

The CS42426 integrated PLL provides a low-jitter system

clock. The internal stereo ADC is capable of independent chan-

nel gain control for single-ended or differential analog inputs.

All six channels of DAC provide digital volume control and dif-

ferential analog outputs. The general purpose outputs may be

driven high or low, or mapped to a variety of DAC mute controls

or ADC overflow indicators.

The CS42426 is ideal for audio systems requiring wide

dynamic range, negligible distortion and low noise, such as A/V

receivers, DVD receivers, digital speaker and automotive audio

systems.

ORDERING INFORMATION

CS42426-CQZ

-10° to 70° C

64-pin LQFP

CS42426-DQZ

-40° to 85° C

64-pin LQFP

CDB42428

Evaluation Board

PLL

Internal Voltage

Reference

RST

GPO1

AD0/CS

SCL/CCLK

SDA/CDOUT

AD1/CDIN

VLC

AOUTA1-

AOUTA3-

AOUTA2-

AOUTB2-

AOUTB1-

AOUTB3-

AINL+

AINL-

AINR+

AINR-

FILT+

REFGND VQ

ADC#1

ADC#2

Digital Filter

Digital Filter

Gain & Clip

Gain & Clip

ADC_SDOUT

ADCIN1

ADCIN2

DAC_SCLK

DAC_LRCK

DAC_SDIN3

DAC_SDIN2

DAC_SDIN1

VLS

ADC_LRCK

DGND VD

OMCK

RMCK

LPFLT

INT

Control

Port

DAC#1

DAC#2

DAC#3

DAC#4

DAC#5

DAC#6

D

ig

it

a

l F

ilt

e

r

V

o

lu

m

e

C

ontr

o

l

GPO2

GPO3

GPO4

GPO5

GPO6

GPO7

MUTEC

Mute

A

nal

og F

ilt

er

VA AGND

ADC

Serial

Audio

Port

Mult/Div

GPO

ADC_SCLK

Lev

el

T

rans

lator

Lev

el

T

rans

la

to

r

DA

C S

e

ri

al

A

udi

o P

o

rt

JUL ‘04

DS604A2