15

CS42426

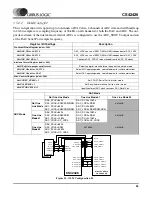

sample rate applications are shown in Table 1. The lock time is the worst case for an Fs transition from un-

locked state to locking to 192 kHz.

It is important to treat the LPFLT pin as a low level analog input. It is suggested that the ground end of the

PLL filter be returned directly to the AGND pin independently of the digital ground plane.

3.4.2

OMCK System Clock Mode

A special clock switching mode is available that allows the clock that is input through the OMCK pin to

be used as the internal master clock. This feature is controlled by the SW_CTRLx bits in register “Clock

Control (address 06h)” on page 37. An advanced auto switching mode is also implemented to maintain

master clock functionality. The clock auto switching mode allows the clock input through OMCK to be

used as a clock in the system without any disruption when the PLL loses lock, for example, when the

LRCK is removed from ADC_LRCK. This clock switching is done glitch free.

3.4.3

Master Mode

In master mode, the serial interface timings are derived from an external clock attached to OMCK or the

output of the PLL with an input reference to the ADC_LRCK input from the ADC serial port. The DAC

Serial Port and ADC Serial Port can both be masters only when OMCK is used as the clock source. When

using the PLL output, the ADC Serial Port must be slave and the DAC Serial Port can operate in Master

Mode. Master clock selection and operation is configured with the SW_CTRL1:0 and CLK_SEL bits in

the Clock Control Register (See “Clock Control (address 06h)” on page 37).

The sample rate to OMCK ratios and OMCK frequency requirements for Master mode operation are

shown in Table 2.

3.4.4

Slave Mode

In Slave mode, DAC_LRCK, DAC_SCLK and/or ADC_LRCK and ADC_SCLK operate as inputs. The

Left/Right clock signal must be equal to the sample rate, Fs and must be synchronously derived from the

supplied master clock, OMCK or must be synchronous to the supplied ADC_LRCK used as the input to

Fs Range (kHz) RFILT (k

Ω

) CFILT (pF) CRIP (pF)

Settling time

32 to 192

10

2700

680

11 ms

Table 1. PLL External Component Values

Sample

Rate

(kHz)

OMCK (MHz)

Single Speed

(4 to 50 kHz)

Double Speed

(50 to 100 kHz)

Quad Speed

(100 to 192 kHz)

256x

384x

512x

128x

192x

256x

64x

96x

128x

48

12.2880

18.4320 24.5760

-

-

-

-

-

-

96

-

-

-

12.2880 18.4320 24.5760

-

-

-

192

-

-

-

-

-

-

12.2880 18.4320 24.5760

Table 2. Common OMCK Clock Frequencies