CS42426

28

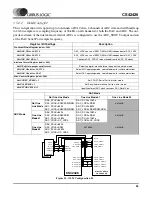

Since the read operation can not set the MAP, an aborted write operation is used as a preamble. As shown

in Figure 19, the write operation is aborted after the acknowledge for the MAP byte by sending a stop con-

dition. The following pseudocode illustrates an aborted write operation followed by a read operation.

Send start condition.

Send 10011xx0 (chip address & write operation).

Receive acknowledge bit.

Send MAP byte, auto increment off.

Receive acknowledge bit.

Send stop condition, aborting write.

Send start condition.

Send 10011xx1(chip address & read operation).

Receive acknowledge bit.

Receive byte, contents of selected register.

Send acknowledge bit.

Send stop condition.

Setting the auto increment bit in the MAP allows successive reads or writes of consecutive registers. Each

byte is separated by an acknowledge bit.

3.7

Interrupts

The CS42426 has a comprehensive interrupt capability. The INT output pin is intended to drive the inter-

rupt input pin on the host microcontroller. The INT pin may be set to be active low, active high or active

low with no active pull-up transistor. This last mode is used for active low, wired-OR hook-ups, with mul-

tiple peripherals connected to the microcontroller interrupt input pin.

Many conditions can cause an interrupt, as listed in the interrupt status register descriptions. See “Interrupt

Status (address 20h) (Read Only)” on page 46. Each source may be masked off through mask register bits.

In addition, each source may be set to rising edge, falling edge, or level sensitive. Combined with the op-

tion of level sensitive or edge sensitive modes within the microcontroller, many different configurations

are possible, depending on the needs of the equipment designer.