CS42426

36

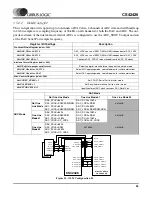

5.6

Misc Control (address 05h)

5.6.1

EXTERNAL ADC SCLK SELECT (EXT ADC SCLK)

Default = 0

Function:

This bit identifies the SCLK source for the external ADCs attached to the ADCIN1/2 ports when using

one line mode of operation.

0 - ADC_SCLK is used as external ADC SCLK.

1 - DAC_SCLK is used as external ADC SCLK.

5.6.2

RMCK HIGH IMPEDANCE (HIZ_RMCK)

Default = 0

Function:

This bit is used to create a high impedance output on RMCK when the clock signal is not required.

5.6.3

FREEZE CONTROLS (FREEZE)

Default = 0

Function:

This function will freeze the previous output of, and allow modifications to be made, to the Volume

Control (address 0Fh-16h), Channel Invert (address 17h) and Mixing Control Pair (address 18h-1Bh)

registers without the changes taking effect until the FREEZE is disabled. To make multiple changes

in these control port registers take effect simultaneously, enable the FREEZE bit, make all register

changes, then disable the FREEZE bit.

5.6.4

INTERPOLATION FILTER SELECT (FILT_SEL)

Default = 0

Function:

This feature allows the user to select whether the DAC interpolation filter has a fast or slow roll off.

For filter characteristics please See “D/A Digital Filter Characteristics” on page 56.

0 - Fast roll off.

1 - Slow roll off.

5.6.5

HIGH PASS FILTER FREEZE (HPF_FREEZE)

Default = 0

Function:

When this bit is set, the internal high-pass filter for the selected channel will be disabled.The current

DC offset value will be frozen and continue to be subtracted from the conversion result. See “A/D Dig-

ital Filter Characteristics” on page 52.

7

6

5

4

3

2

1

0

Ext ADC SCLK

HiZ_RMCK

Reserved

FREEZE

FILT_SEL

HPF_FREEZE

DAC_SP

M/S

ADC_SP

M/S