CS42426

34

5.4.2

ADC FUNCTIONAL MODE (ADC_FMX)

Default = 00

00 - Single-Speed Mode (4 to 50 kHz sample rates)

01 - Double-Speed Mode (50 to 100 kHz sample rates)

10 - Quad-Speed Mode (100 to 192 kHz sample rates)

11 - Reserved

Function:

Selects the required range of sample rates for the ADC serial port(ADC_SP). These bits must be set

to the corresponding sample rate range when the ADC_SP is in Master or Slave mode.

5.4.3

ADC CLOCK SOURCE SELECT (ADC_CLK SEL)

Default = 0

0 - ADC_SDOUT clocked from the DAC_SP.

1 - ADC_SDOUT clocked from the ADC_SP.

Function:

Selects the desired clocks for the ADC serial output.

5.4.4

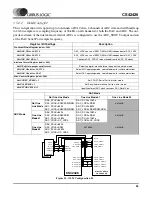

DAC DE-EMPHASIS CONTROL (DAC_DEM)

Default = 0

Function:

Enables the digital filter to maintain the standard 15

µ

s/50

µ

s digital de-emphasis filter response at

the auto-detected sample rate of either 32, 44.1, or 48 kHz. De-emphasis will not be enabled, regard-

less of this register setting, at any other sample rate. If the FRC_PLL_LK bit is set to a ‘1’b, then the

auto-detect sample rate feature is disabled. To apply the correct de-emphasis filter, use the DE-

EMPH bits in the Interrupt Control (address 1Eh) register to set the appropriate sample rate.

5.5

Interface Formats (address 04h)

5.5.1

DIGITAL INTERFACE FORMAT (DIFX)

Default = 01

Function:

These bits select the digital interface format used for the ADC & DAC Serial Port when not in one_line

mode. The required relationship between the Left/Right clock, serial clock and serial data is defined by

the Digital Interface Format and the options are detailed in Figures 7 - 9.

DAC_DEM

reg03h[1]

FRC_PLL_LK

reg06h[0]

DE-EMPH[1:0]

reg1Eh[5:4]

De-Emphasis

Mode

0

X

XX

No De-Emphasis

1

0

XX

Auto-Detect Fs

1

1

00

01

10

11

Reserved

32 kHz

44.1 kHz

48 kHz

Table 6. DAC De-Emphasis

7

6

5

4

3

2

1

0

DIF1

DIF0

ADC_OL1

ADC_OL0

DAC_OL1

DAC_OL0

Reserved

CODEC_RJ16