37

CS42426

5.6.6

DAC SERIAL PORT MASTER/SLAVE SELECT (DAC_SP M/S)

Default = 1

Function:

In Master mode, DAC_SCLK and DAC_LRCK are outputs. Internal dividers will divide the master

clock to generate the serial clock and left/right clock. In Slave mode, DAC_SCLK and DAC_LRCK

become inputs.

5.6.7

ADC SERIAL PORT MASTER/SLAVE SELECT (ADC_SP M/S)

Default = 1

Function:

In Master mode, ADC_SCLK and ADC_LRCK are outputs. Internal dividers will divide the master

clock to generate the serial clock and left/right clock. In Slave mode, ADC_SCLK and ADC_LRCK

become inputs.

To use the PLL to lock to ADC_LRCK, the ADC_SP must be in slave mode. When using the PLL to

lock to LRCK, if ADC_SDOUT is configured to be clocked by the ADC_SP, then both ADC_SCLK and

ADC_LRCK must be present. If ADC_SDOUT is configured to be clocked by the DAC_SP, then only

the ADC_LRCK signal must be applied.

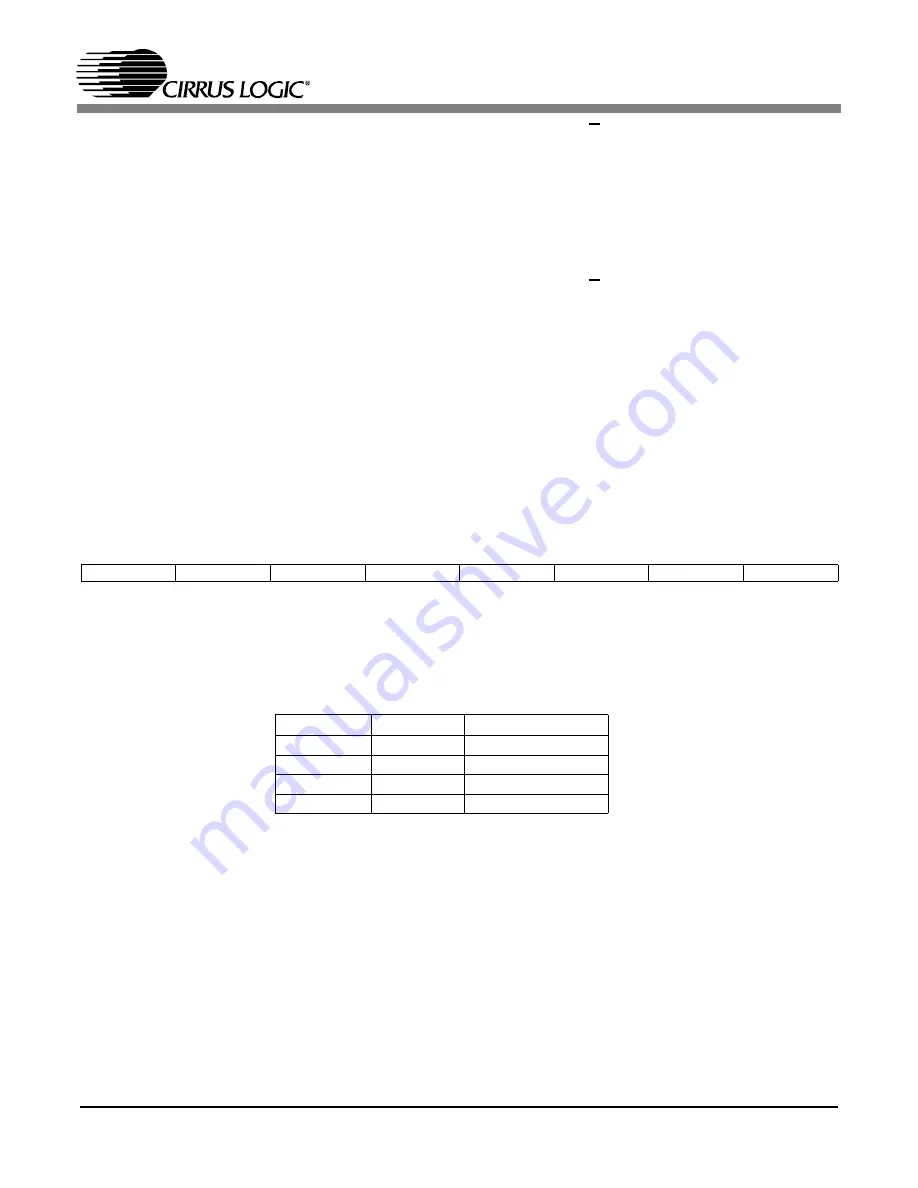

5.7

Clock Control (address 06h)

5.7.1

RMCK DIVIDE (RMCK_DIVX)

Default = 00

Function:

Divides/multiplies the internal MCLK, either from the PLL or OMCK, by the selected factor.

7

6

5

4

3

2

1

0

RMCK_DIV1

RMCK_DIV0

OMCK Freq1

OMCK Freq0

PLL_LRCK

SW_CTRL1

SW_CTRL0

FRC_PLL_LK

RMCK_DIV1 RMCK_DIV0

Description

0

0

Divide by 1

0

1

Divide by 2

1

0

Divide by 4

1

1

Multiply by 2

Table 10. RMCK Divider Settings