DS632F1

21

CS44800

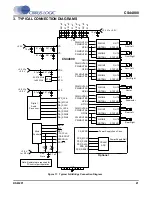

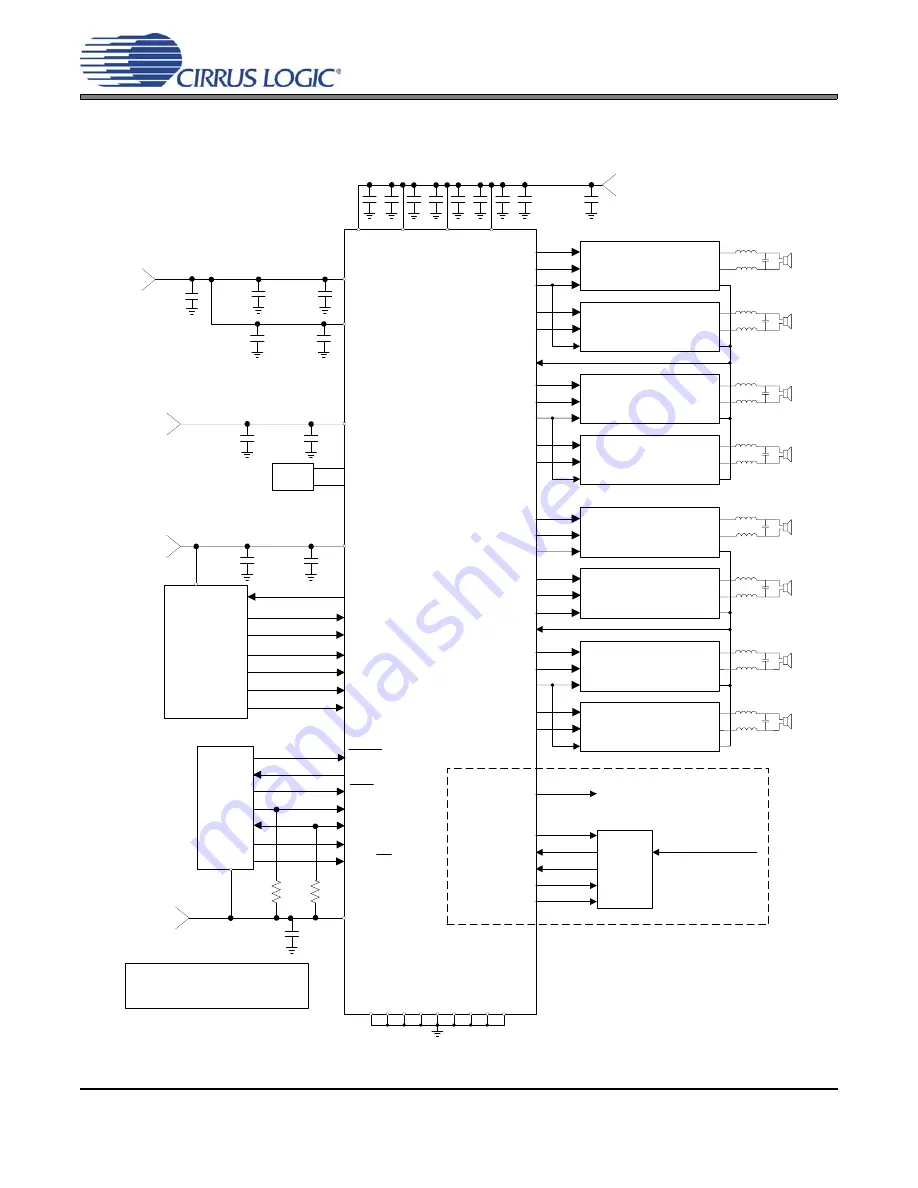

3. TYPICAL CONNECTION DIAGRAMS

P

PWMOUTA1-

P

PWMOUTB1-

GND

PWM IN1

OUT1

CONTROL

P

PWMOUTA2-

P

PWMOUTB2-

P

PWMOUTA3-

P

PWMOUTB3-

P

PWMOUTA4-

P

PWMOUTB4-

PSR_DATA

PSR_SYNC

PSR_MCLK

CS4461

ADC

Power Supply Rail

Front Left

Surr. Left

Surr. Right

Center

Subwoofer

Rear Left

Rear Right

GPIO1

GPIO2

GPIO4

PSR_RESET

PSR_EN

PS_SYNC

Power Supply Sync Clock

GPIO0

STATUS

PWM IN2

OUT2

CONTROL

Front Right

STATUS

PWM IN3

OUT3

CONTROL

STATUS

PWM IN4

OUT4

CONTROL

STATUS

PWM IN5

OUT5

CONTROL

STATUS

PWM IN6

OUT6

CONTROL

STATUS

GPIO3

PWM IN7

OUT7

CONTROL

STATUS

PWM IN8

OUT8

CONTROL

STATUS

GPIO5

GPIO6

Optional

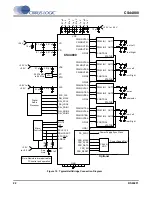

VD

VLC

0.1 µF

+2.5 V

to +5.0 V

SCL/CCLK

SDA/CDOUT

AD1/CDIN

RST

2 k

Ω

2 k

Ω

Note: Resistors are required for

I²C control port operation

See

Note

DAI_SDIN1

DAI_SDIN3

DAI_SDIN2

DAI_LRCK

DAI_SCLK

AD0/CS

INT

Digital

Audio

Processor

Micro-

Controller

DAI_MCLK

VD

SYS_CLK

MUTE

VDX

XTAL

24.576 MHz

to 54 MHz

XTI

XTO

VLS

+2.5 V

+

10 µF

0.1 µF

0.1 µF

0.01 µF

0.01 µF

+3.3 V to

+5.0 V

0.1 µF

0.01 µF

+2.5 V to

+5.0 V

0.1 µF

0.01 µF

+3.3 V to +5.0 V

VDP

0.

01 µF

10 µF

0.1 µF

0.01 µF

0.1

µF

0.0

1

µF

0.

1

µ

F

0.

01 µF

0.1 µF

Figure 11. Typical Full-Bridge Connection Diagram

CS44800