10

DS726PP2

CS4525

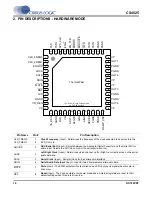

2. PIN DESCRIPTIONS - HARDWARE MODE

Pin Name

Pin #

Pin Description

CLK_FREQ0

CLK_FREQ1

1

2

Clock Frequency

(Input)

- Determines the frequency of the clock expected to be driven into the

SYS_CLK pin.

ADC/SP

3

ADC/Serial Port

(Input)

- Selects between the Analog to Digital Converter and the Serial Port for

audio input. Selects the ADC when high or the serial port when low.

LRCK

4

Left Right Clock

(

Input

) - Determines which channel, Left or Right, is currently active on the serial

audio data line.

SCLK

5

Serial Clock

(

Input

)

-

Serial bit clock for the serial audio interface.

SDIN

6

Serial Audio Data Input

(

Input

) - Input for two’s complement serial audio data.

MUTE

7

Mute

(

Input

) - The PWM outputs will output silence as a 50% duty cycle signal when this pin is

driven low.

RST

8

Reset

(

Input

) - The device enters a low power mode and all internal registers are reset to their

default settings when this pin is driven low.

Top-Down (Through Package) View

48-Pin QFN Package

12

7

6

5

4

3

2

1

11

10

9

8

25

30

31

32

33

34

35

36

26

27

28

29

14

13

15

16

17

18

19

20

21

22

23

24

47

48

46

45

44

43

42

41

40

39

38

37

CLK_FREQ0

CLK_FREQ1

ADC/SP

LRCK

SCLK

SDIN

MUTE

RST

LVD

DGND

VD_REG

VD

VP

OUT1

PGND

PGND

OUT2

VP

VP

OUT3

PGND

PGND

OUT4

VP

VA

_

R

E

G

AGN

D

FI

L

T

+

VQ

AFIL

TL

AF

IL

TR

AINL

AIN

R

OC

REF

PGND

PGND

RAMP_C

AP

TSTI

TST

O

SYS_CLK

I2S/LJ

EN_TFB

ERROC

ERRUVTE

TWR

TST

O

TST

O

PGND

PGND

Thermal Pad