22

DS726PP2

CS4525

AUX SERIAL AUDIO I/O PORT SWITCHING SPECIFICATIONS

AGND = DGND = PGND = 0 V; T

A

= 25°C; VD = 3.3 V; AUX_SDOUT & DLY_SDOUT C

L

= 15 pF; Inputs:

Logic 0 = DGND; Logic 1 = VD;

Notes:

11. F

CLK

is the frequency of the crystal connected to the XTI/XTO pins or the input SYS_CLK signal.

T

CLK

= 1/F

CLK

.

12. F

SI

is the frequency of the input LRCK signal. T

SI

= 1/F

SI

13. May vary during normal operation.

14. F

SCLKI

is the frequency of the input SCLK signal. T

SCLKI

= 1/F

SCLKI

.

Parameters

Symbol Min

Typ

Max

Units

Input Source: Analog Inputs (Internal ADC)

Output Sample Rate

ClkFreq[1:0] = ‘00’

ClkFreq[1:0] = ‘01’

ClkFreq[1:0] = ‘10’

F

SO

-

-

-

F

CLK

/384

F

CLK

/512

F

CLK

/512

-

-

-

Hz

Hz

Hz

AUX_LRCK Duty Cycle

-

50

-

%

AUX_LRCK Period

-

1/F

SO

-

s

AUX_SCLK Frequency

ClkFreq[1:0] = ‘00’

ClkFreq[1:0] = ‘01’

ClkFreq[1:0] = ‘10’

F

SCLKO

-

-

-

48*F

SO

64*F

SO

64*F

SO

-

-

-

Hz

Hz

Hz

AUX_SCLK Duty Cycle

-

50

-

%

AUX_SCLK Period

-

1/F

SCLKO

-

s

Input Source: Serial Audio Input Port

Output Sample Rate

F

S-In

= 32kHz, 44.1 kHz, 48 kHz

F

S-In

= 96 kHz

F

SO

-

-

F

SI

F

SI

/2

-

-

Hz

Hz

AUX_LRCK Duty Cycle

45

-

55

%

AUX_LRCK Period

(

)

T

SI

- T

CLK

T

SI

T

SI

+ T

CLK

s

AUX_SCLK Frequency

F

S-In

= 32kHz, 44.1 kHz, 48 kHz

F

S-In

= 96 kHz

-

-

F

SCLKI

F

SCLKI

/2

-

-

Hz

Hz

AUX_SCLK Duty Cycle

30

-

70

%

AUX_SCLK Period

F

S-In

= 32kHz, 44.1 kHz, 48 kHz

)

F

S-In

= 96 kHz

T

SCLKI

- T

CLK

2*T

SCLKI

- T

CLK

T

SCLKI

2*T

SCLKI

T

SCLKI

+ T

CLK

2*T

SCLKI

+ T

CLK

s

s

Input Source: Analog Inputs or Serial Audio Input Port

AUX_LRCK Rising Edge to AUX_SCLK Falling Edge

t

LTSF

-

-

20

ns

AUX_SCLK Rising Edge to Data Output Valid

t

SRDV

-

-

T

CLK

+ 20

ns

DLY_SDIN Setup Time Before AUX_SCLK Rising Edge

t

DIS

25

-

-

ns

DLY_SDIN Hold Time After AUX_SCLK Rising Edge

t

DIH

10

-

-

ns

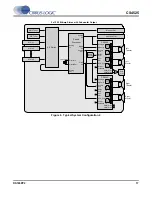

AUX_LRCK

AUX_SCLK

AUX_SDOUT

DLY_SDOUT

DLY_SDIN

MSB

MSB

MSB - 1

MSB - 1

LSB

LSB

t

LTSF

t

SRDV

t

DISU

t

DIH

Figure 8. AUX Serial Port Interface Master Mode Timing