DS726PP2

33

CS4525

6.1.4.6

Parametric EQ

The CS4525 implements 5 fully programmable parametric EQ filters.

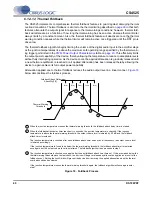

The filters are implemented in the bi-quad form shown below.

This architecture is represented by the equation shown below where y[n] represents the output sample

value and x[n] represents the input sample value.

Equation 1. Bi-Quad Filter Equation

The coefficients are represented in binary form by 24-bit signed values stored in 3.21 two’s complement

format. The 3 MSB’s represent the sign bit and the whole-number portion of the decimal coefficient, and

the 21 LSB’s represent the fractional portion of the decimal coefficient. The coefficient values must be in

the range of -4.00000 decimal (80 00 00 hex) to 3.99996 decimal (7F FF FF hex).

The binary coefficient values are stored in registers 0Ah - 54h. Each 24-bit coefficient is split into 3 bytes,

each of which is mapped to an individually accessible register location. See the

ence” section beginning on page 66

for the specific register locations for each coefficient.

By default, all b

0

coefficients are set to 1 decimal, and all other coefficients are set to 0 decimal. This im-

plements a pass-through function.

The parametric equalizers be independently enabled and disabled for channels A and B with the En-

ChAPEq and EnChBPEq bits located in the EQ Config register.

Referenced Control

Register Location

EnChAPEq ..........................

“Enable Channel A Parametric EQ (EnChAPEq)” on page 79

EnChBPEq ..........................

“Enable Channel B Parametric EQ (EnChBPEq)” on page 79

b

0

b

1

b

2

a

1

a

2

Z

-1

Z

-1

Z

-1

Z

-1

x[n]

y[n]

Figure 16. Bi-Quad Filter Architecture

y[n] = b

0

x[n] + b

1

x[n-1] + b

2

x[n-2] + a

1

y[n-1] + a

2

y[n-2]