42

DS726PP2

CS4525

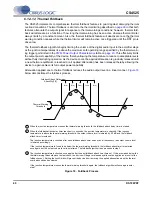

The sensitivity level of the high- and low-pass outputs of the crossovers can be independently adjusted

from 0 dB to -7.5 dB in 0.5 dB increments. The maximum attenuation level of -7.5 dB will compensate for

an approximate 4 dB difference in sound pressure level (SPL) between the tweeter and the mid-

range/woofer drivers. The sensitivity is adjusted using the HighPass[3:0] and LowPass[3:0] bits in the

Sensitivity register. Note that these bits affect the sensitivity of both channel A and channel B high- and

low-pass outputs.

The 2-way crossover can be enabled by setting the En2Way bit in the Volume Cfg register.

X-Over Freq 5

3.0 kHz

2.88 kHz

3.13 kHz

X-Over Freq 6

3.2 kHz

3.07 kHz

3.34 kHz

X-Over Freq 7

3.4 kHz

3.26 kHz

3.55 kHz

Referenced Control

Register Location

En2Way...............................

“Enable 2-Way Crossover (En2Way)” on page 81

2WayFreq[2:0].....................

“2-Way Cross-Over Frequency (2WayFreq[2:0])” on page 81

HighPass[3:0]......................

“Channel A and Channel B High-Pass Sensitivity Adjust (HighPass[3:0])” on page 82

LowPass[3:0].......................

“Channel A and Channel B Low-Pass Sensitivity Adjust (LowPass[3:0])” on page 81

Input Sample Rate

32 kHz

44.1 kHz

48 kHz, 96 kHz

Table 5. 2-Way Cross-Over Frequencies