DS726PP2

43

CS4525

6.1.5

Auxiliary Serial Output

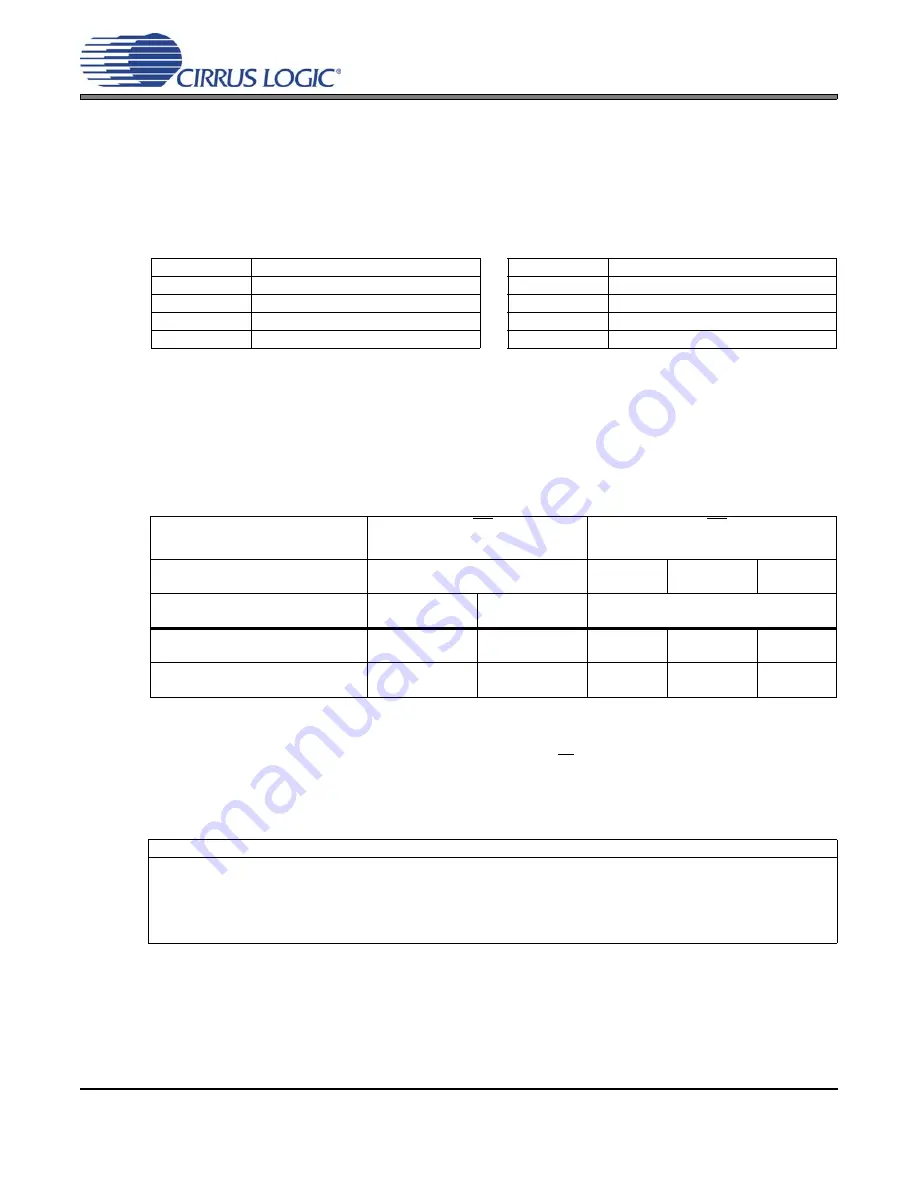

The CS4525 includes a stereo auxiliary serial output which allows an external device to leverage on its

internal signal processing and routing capabilities. The auxiliary serial output can receive its data from any

of the sources shown in the

The supported output data routing configurations are shown in

below. By default, the serial port

is configured to output channels A and B on the auxiliary output data left and right channels respectively.

The data output on each channel of AUX_SDOUT is set by the LChDSel[1:0] and RChDSel[1:0] bits in

the Aux Port Configuration register. The frequencies of AUX_LRCK and AUX_SCLK will vary based upon

the whether the serial input or analog input is being used and the frequency of the system clock for the

CS4525; the nominal values for these clocks are listed in

. The characteristics of AUX_SCLK,

AUX_LRCK, and AUX_SDOUT are described in the

AUX Serial Audio I/O Port Switching Specifications

table on

The auxiliary port can be enabled using the EnAuxPort bit. When enabled, the port operates as a master

and clocks out data in the format dictated by the AuxI²S/LJ bit. When disabled, the AUX_LRCK,

AUX_SCLK, and AUX_SDOUT pins continuously drive a logic ‘0’. It should be noted that when the

CS4525 is configured for analog input, the AUX_LRCK, AUX_SCLK, and AUX_SDOUT pins will contin-

uously drive a logic ‘0’ if either the PDnADC bit or PDnAll bit is set.

LChDSel[1:0]

Aux Left Channel Data

RChDSel[1:0]

Aux Right Channel Data

00

Channel A

00

Channel A

01

Channel B

01

Channel B

10

Sub Channel

10

Sub Channel

11

Channel B X-Over LPF

11

Channel B X-Over HPF

Table 6. Auxiliary Serial Port Data Output

Signal

ADC/SP = 0

(Digital Input Mode)

ADC/SP = 1

(Analog Input Mode)

Applied System Clock from either

SYS_CLK or External Crystal

18.432, 24.576, or 27.000MHz

18.432MHz

24.576MHz

27.000MHz

Frequency of LRCK Input

32kHz, 44.1kHz,

or 48kHz

96kHz

Not Applicable

Nominal Frequency of AUX_SCLK

Output

Frequency of

SCLK Input

Frequency of

SCLK Input / 2

2.304MHz

3.072MHz

3.375MHz

Nominal Frequency of AUX_LRCK

Output

Frequency of

LRCK Input

Frequency of

LRCK Input / 2

48kHz

48kHz

52.734kHz

Table 7. Nominal Switching Frequencies of the Auxiliary Serial Output

Referenced Control

Register Location

EnAuxPort ...........................

“Enable Aux Serial Port (EnAuxPort)” on page 72

LChDSel[1:0].......................

“Aux Serial Port Left Channel Data Select (LChDSel[1:0])” on page 73

RChDSel[1:0] ......................

“Aux Serial Port Right Channel Data Select (RChDSel[1:0])” on page 72

AuxI²S/LJ.............................

“Aux/Delay Serial Port Digital Interface Format (AuxI²S/LJ)” on page 72

PDnADC..............................

“Power Down ADC (PDnADC)” on page 88

PDnAll .................................