DS726PP2

45

CS4525

6.1.7

Powered PWM Outputs

The CS4525’s 3 internal modulators can be used to generate multiple powered PWM output configura-

tions to enable a wide variety of system implementations. The CS4525 also implements PWM Popguard

to minimize output transients in half-bridge configurations.

6.1.7.1

Output Channel Configurations

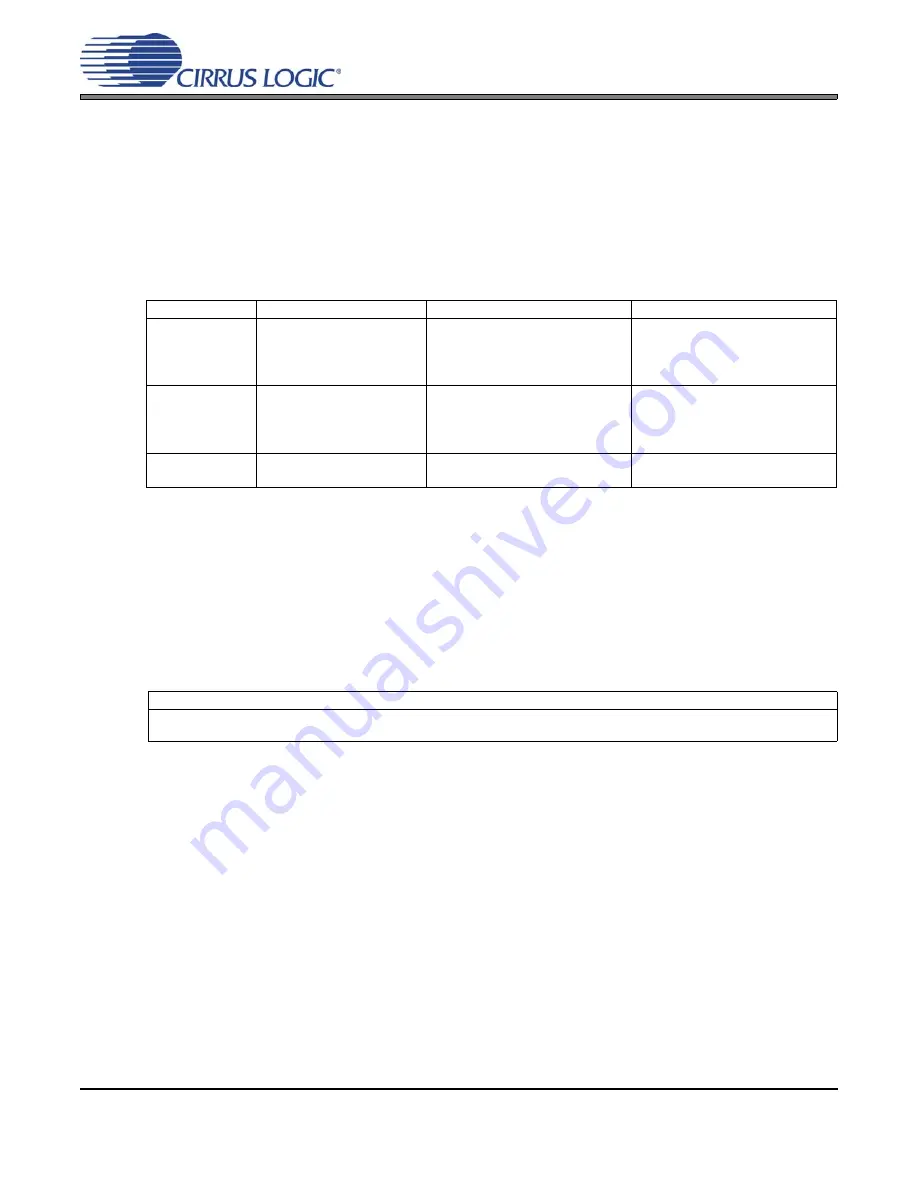

Three PWM power output configurations are supported as shown in

below. The configurations

support stereo full-bridge, stereo half-bridge with full-bridge sub, and mono parallel full-bridge output.

The configurations are selected by the OutputCfg[1:0] bits in the Output Cfg register and must only be

changed when the device is in power-down mode (the PDnAll bit is set). Any attempt to write the Out-

putCfg[1:0] bits while the device is powered-up will be ignored.

It should be noted that signals on channels 1, 2 and the sub channel are dependent upon the digital sound

processing blocks being used. For instance, if the 2-way crossover is enabled, channel 1 and 2 contain

the 2-way crossover channel A high- and low-pass outputs respectively. For more information, see the

section and

6.1.7.2

PWM Popguard Transient Control

The CS4525 uses Popguard technology to minimize the effects of power-up and power-down output tran-

sients commonly produced by half-bridge, single supply amplifiers implemented with external DC-block-

ing capacitors connected in series with the audio outputs.

PWM Popguard operates by linearly ramping the PWM power outputs up to and down from their bias point

of VP/2 when a channel is powered up and down respectively using the PDnOutX or PDnAll bits. This

OutputCfg[1:0]

Power Configuration

Output Signal

Output Pin(s)

00

2 Ch. Full-Bridge

Channel 1 +

Channel 1 -

Channel 2 +

Channel 2 -

OUT1

OUT2

OUT3

OUT4

01

2 Ch. Half-Bridge

+

1 Ch. Full-Bridge

Channel 1 +

Channel 2 +

Sub C

Sub Channel -

OUT1

OUT2

OUT3

OUT4

10

1 Ch. Parallel Full-Bridge

Channel 1 +

Channel 1 -

OUT1, OUT2

OUT3, OUT4

Table 8. PWM Power Output Configurations

Referenced Control

Register Location

OutputCfg[1:0].....................

“Output Configuration (OutputCfg[1:0])” on page 73

PDnAll .................................