DS726PP2

55

CS4525

6.2.2.2

Recommended Power-Down Sequence

1.

Bring MUTE low to mute the device’s outputs and minimize audible pops.

2.

Bring RST low to halt the operation of the device.

The device’s power consumption will be brought to an absolute minimum.

3.

Remove power.

6.2.3

Input Source Selection

The CS4525 can accept analog or digital audio input signals. Digital audio input signals are supplied

through the serial audio input port as outlined in

“Serial Audio Interfaces” on page 62

. Analog audio input

signals are supplied through the internal ADC as outlined in

. The input source

is selected by the ADC/SP pin as shown in

below and can be changed at any time without caus-

ing any audible pops or clicks.

In hardware mode, the serial audio input port supports both I²S and left-justified formats. The serial audio

interface format is selected by the I2S/LJ pin as shown in

below.

6.2.4

PWM Channel Delay

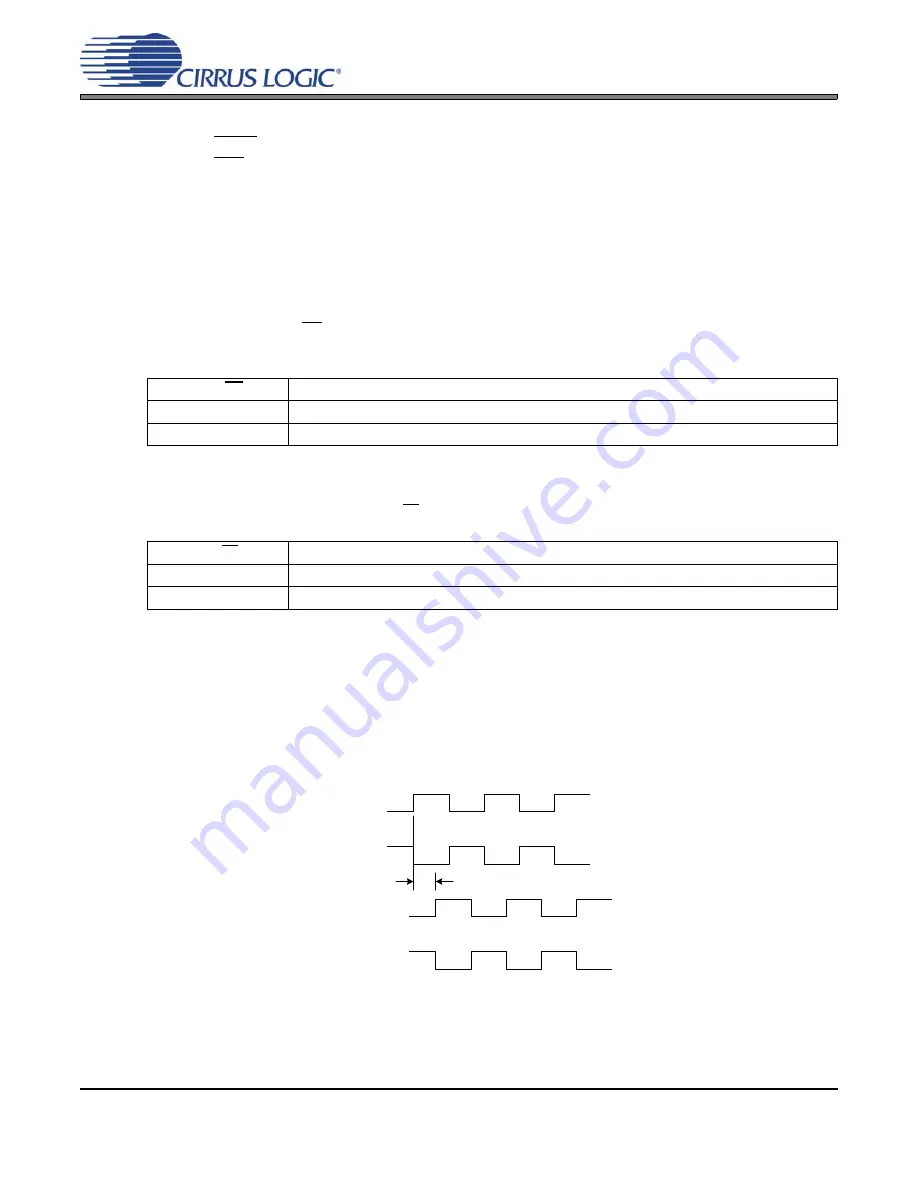

In hardware mode, the CS4525 offsets the PWM switching edges between channels as a method of man-

aging switching noise and reducing radiated emissions.

The OUT3/OUT4 signal pair is delayed from the OUT1/OUT2 signal pair by 4 SYS_CLK cycles as shown

in

below. The absolute delay time is calculated by multiplying the period SYS_CLK by 4.

ADC/SP

Selected Input Source

Low

Digital Audio Inputs (Serial Port)

High

Analog Audio Inputs (ADC)

Table 14. Input Source Selection

I2S/LJ

Selected Serial Audio Interface Format

Low

Left-Justified

High

I²S

Table 15. Serial Audio Interface Format Selection

OUT1

OUT2

4 x T

SYS_CLK

OUT3

OUT4

Figure 23. Hardware Mode PWM Output Delay