62

DS726PP2

CS4525

6.6

Serial Audio Interfaces

The CS4525 interfaces to external digital audio devices via the serial audio input port and the auxiliary/delay

serial ports.

The serial audio input port provides support for I²S, Left-Justified and Right-Justified data formats and op-

erates in slave mode only, with LRCK and SCLK as inputs. The input LRCK signal must be equal to the

sample rate, Fs and must be synchronous to the serial bit clock, SCLK, which is used to sample the data

bits.

The auxiliary/delay serial port (available in software mode only) supports I²S and Left-Justified data formats

and operates in master mode only, with AUX_LRCK and AUX_SCLK as outputs.

Each of the supported formats is described in detail in sections

below. Please refer to the

Audio Input Port Switching Specifications

and

AUX Serial Audio I/O Port Switching Specifications

on

(respectively) for the precise timing and tolerances of each signal.

For additional information, application note AN282 presents a tutorial of the 2-channel serial audio interface.

AN282 can be downloaded from the Cirrus Logic web site at

.

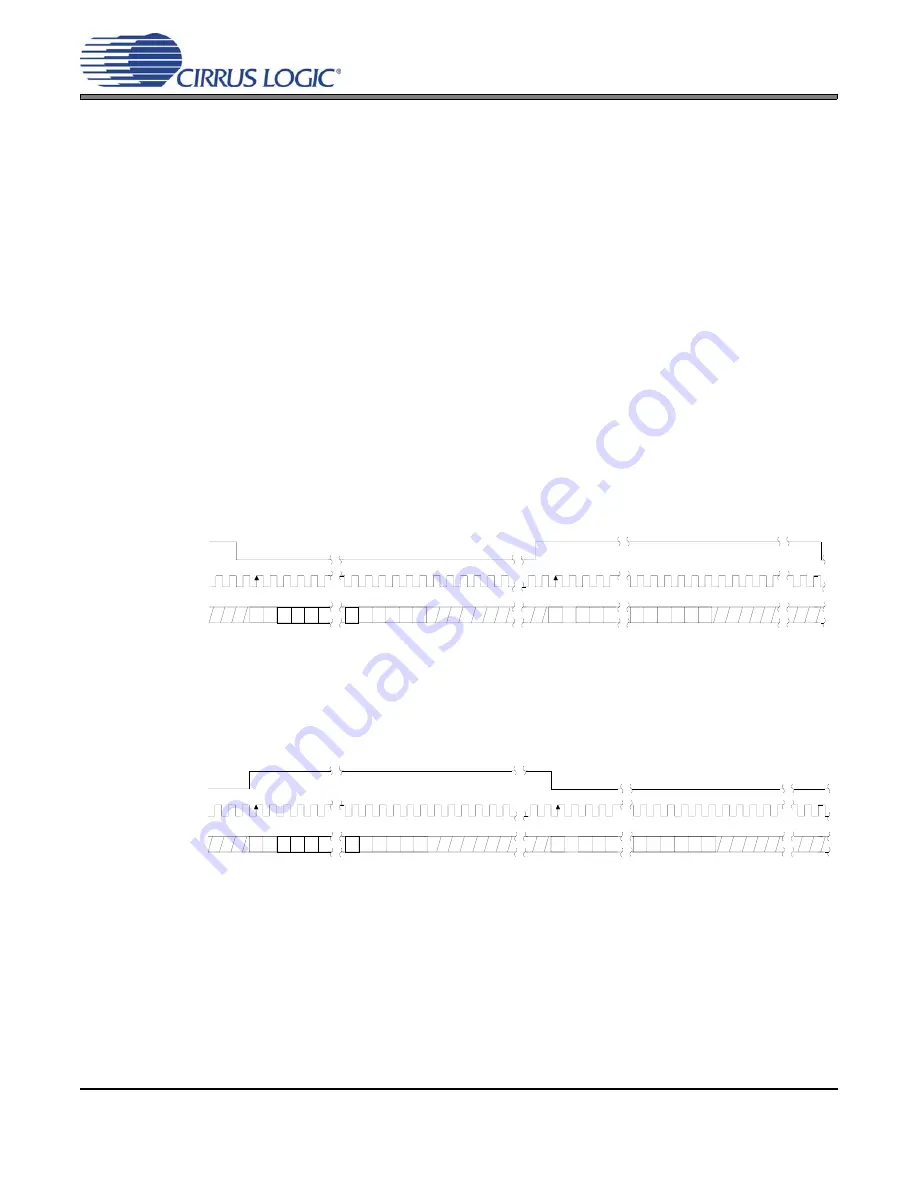

6.6.1

I²S Data Format

In I²S format, data is received most significant bit first one SCLK delay after the transition of LRCK and is

valid on the rising edge of SCLK. The left channel data is presented when LRCK is low; the right channel

data is presented when LRCK is high.

6.6.2

Left-Justified Data Format

In Left-Justified format, data is received most significant bit first on the first SCLK after a LRCK transition

and is valid on the rising edge of SCLK. The left channel data is presented when LRCK is high and the

right channel data is presented when LRCK is low.

Left Channel

Right Channel

SDIN

+3 +2 +1

+5 +4

-1 -2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 -3 -4

MSB

MSB

LSB

LSB

LRCK

SCLK

Figure 30. I²S Serial Audio Formats

LRCK

SCLK

Left Channel

Right Channel

SDIN

+3 +2 +1

+5 +4

-1 -2 -3 -4 -5

+3 +2 +1

+5 +4

-1 -2 -3 -4

MSB

LSB

MSB

LSB

Figure 31. Left-Justified Serial Audio Formats