DS726PP2

89

CS4525

the channel output configuration selected. When transitioning from normal operation to power down, the

specific output will power down according to the state of the RmpSpd[1:0] bits and the channel output con-

figuration selected.

The entire divide will enter a low-power state when this function is enabled:

9.19.6

Power Down (PDnAll)

Default = 1

Function:

The CS4525 will enter a power-down state when this function is enabled:

1.

The power PWM outputs will be held in a high-impedance state.

2.

The logic-level PWM outputs will continuously drive a logic ‘0’ if the HiZPSig bit is set and will be held

in a high-impedance state if the HiZPSig bit is clear.

3.

AUX_SDOUT, the auxiliary serial data output, will be driven to a digital-low. AUX_LRCK and

AUX_SCLK, the auxiliary serial output’s clocks, will continue to operate if the EnAuxPort bit is set,

ADC/SP is cleared, and the serial audio input receives a valid SCLK and LRCK; otherwise they will

also be driven to a digital-low voltage.

4.

DLY_SDOUT, the delay serial data output, will output the unprocessed audio data from SDATA if

EnAuxPort is set, DlyPortCfg[1:0] is configured for serial output delay interface, ADC/SP is cleared,

and the serial audio input port receives a valid SCLK, LRCK, and SDATA. Otherwise, it will drive a

low voltage.

The contents of the control registers are retained in this state. Once the PDnAll bit is disabled, the pow-

ered and logic-level PWM outputs will first perform a click-free start-up function and then resume normal

operation.

The PDnAll bit defaults to ‘enabled’ on power-up and must be disabled before normal operation can occur.

9.20

Interrupt (Address 60h)

Bits [7:4] in this register are read only. A ‘1’b in these bit positions indicates that the associated condition has oc-

curred at least once since the register was last read. A ‘0’b indicates that the associated condition has not occurred

since the last reading of the register. Reading the register resets bits to [7:4] ‘0’b. These bits are considered “edge-

triggered” events. The operation of these 4 bits is not affected by the interrupt mask bits and the condition of each

bit can be polled instead of generating an interrupt as required.

9.20.1

SRC Lock State Transition Interrupt (SRCLock)

Function:

This bit is read only. When set, indicates that the SRC has transitioned from an unlock to lock state or

from a lock state to an unlock state since the last read of this register. Conditions which cause the SRC

to transition states, such as loss of LRCK, SCLK, an LRCK ratio change, or the SRC achieving lock, will

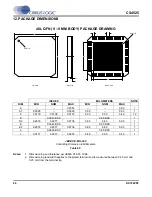

PDnChX Setting

Power Output X Power-Down State

0 .......................................... Normal power output X operation.

1 .......................................... Power output X power-down enabled.

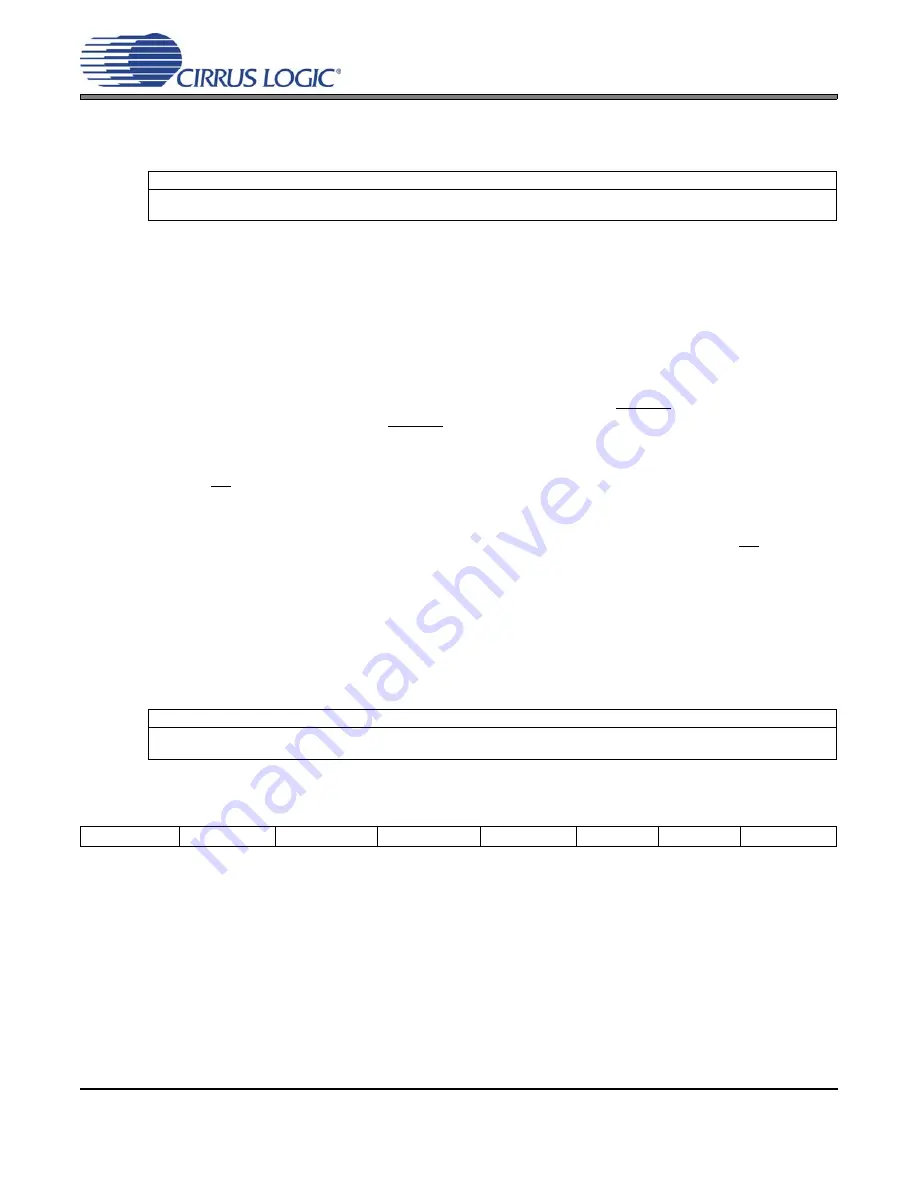

PDnAll Setting

Device Power-Down State

0 .......................................... Normal device operation.

1 .......................................... Device power-down enabled.

7

6

5

4

3

2

1

0

SRCLock

ADCOvfl

ChOvfl

AmpErr

SRCStateM

ADCOvflM

ChOvflM

AmpErrM