3-14

Copyright 2009 Cirrus Logic, Inc.

DS734UM7

SPI Port

CS485xx Hardware User’s Manual

3.3.1 SPI System Bus Description

The SPI bus is a multi-master bus. This means that more than one device capable of controlling the bus can

be connected to it. Generation of clock signals on the SPI bus is always the responsibility of master devices;

each master generates its own clock signals when transferring data on the bus. Bus clock signals from a

master cannot be altered by any other device on the bus, otherwise a collision will occur. The slave chip-

select signals can only be controlled by master devices.

SCP_MOSI (Master Out/Slave In) and SCP_MISO (Master In/Slave Out) are bidirectional lines that change

their behavior depending on whether the device is operating in master or slave mode. Only the master can

drive the MOSI signal while only the slave can drive the MISO signal.

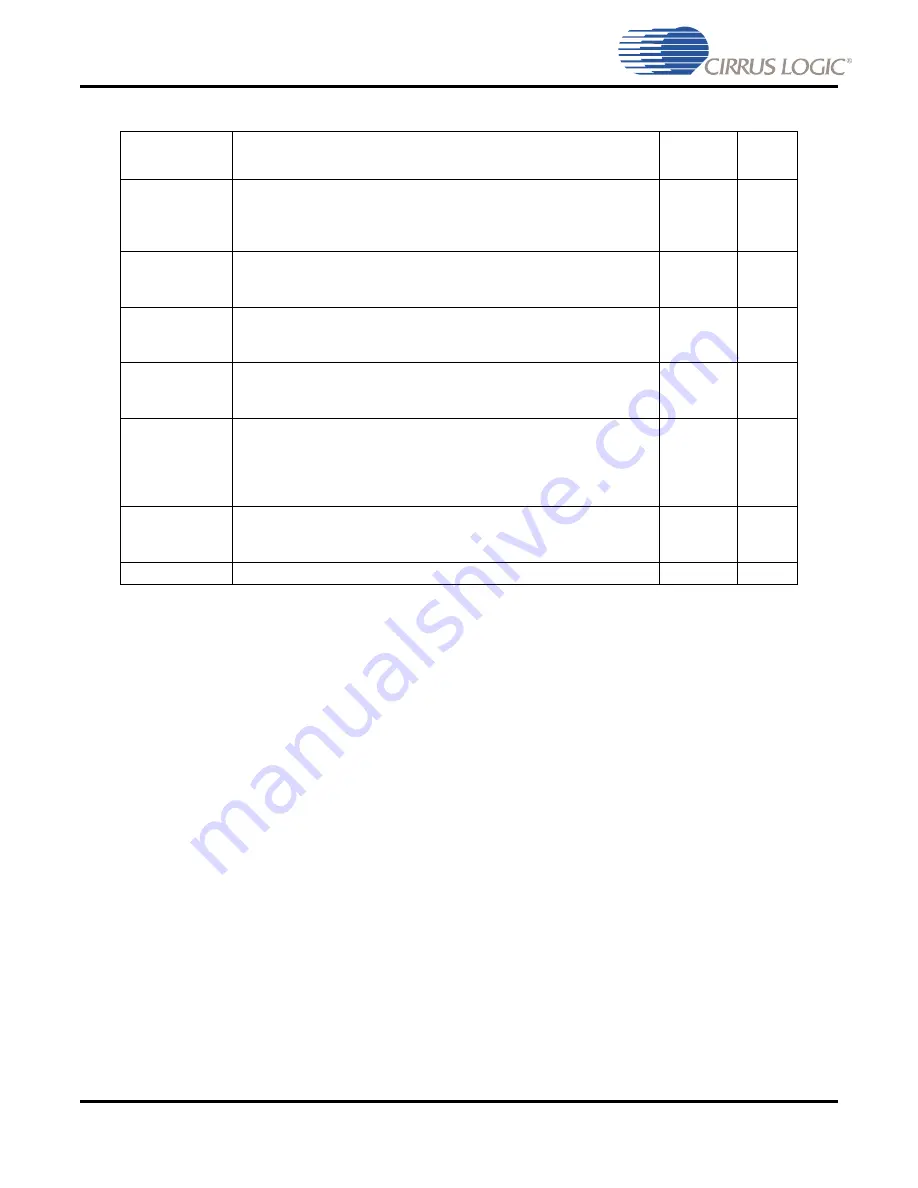

Table 3-2. Serial Control Port SPI Signals

Pin Name

Pin Description

LQFP-48

Pin #

Pin

Type

SCP_CS

SPI Chip Select, Active Low

In serial SPI slave mode, this pin is used as the active-low chip-select

input signal. In SPI serial master mode, if this pin is driven low by

another master device on the bus, it will cause a mode fault to occur.

38

Input

SCP_CLK

SPI Control Port Bit Clock

In master mode, this pin serves as the serial control clock output. In

serial slave mode, this pin serves as the serial control clock input.

36

I/O

SCP_MOSI

SPI Mode Master Data Output/Slave Data Input

SCP_MOSI in SPI slave mode this pin serves an the data input, in SPI

master mode this pin serves as the data output.

34

I/O

SCP_MISO

SPI Mode Master Data Input/Slave Data Output

In SPI slave mode this pin serves as the data input. In SPI master

mode this pin serves as the data output.

35

I/O

SCP_IRQ

Serial Control Port Data Ready Interrupt Request Output, Active Low

This pin is driven low when the DSP has a message for the host to

read. The pin will go high when the host has read the message and the

DSP has no further messages. This pin reflects the state of the SCP

port Transmit Buffer Empty Flag.

39

Open

Drain

SCP_BSY

Serial Control Port Input Busy, Output, Active Low

This pin is driven low when the control port’s receive buffer is full. This

pin reflects the state of the SCP or PCP Receive Buffer Full Fag.

41

Open

Drain

EE_CS

Master Mode Serial EPROM Chip Select, Active Low

41

Output