3-19

Copyright 2009 Cirrus Logic, Inc.

DS734UM7

SPI Port

CS485xx Hardware User’s Manual

When performing a SPI read, the same protocol is used whether reading a single byte or multiple bytes.

From a hardware perspective, it makes no difference whether communication is a single byte or multiple

bytes of any message length, so long as the correct hardware protocol is followed. The example shown in

this section can be generalized to fit any SPI read situation.

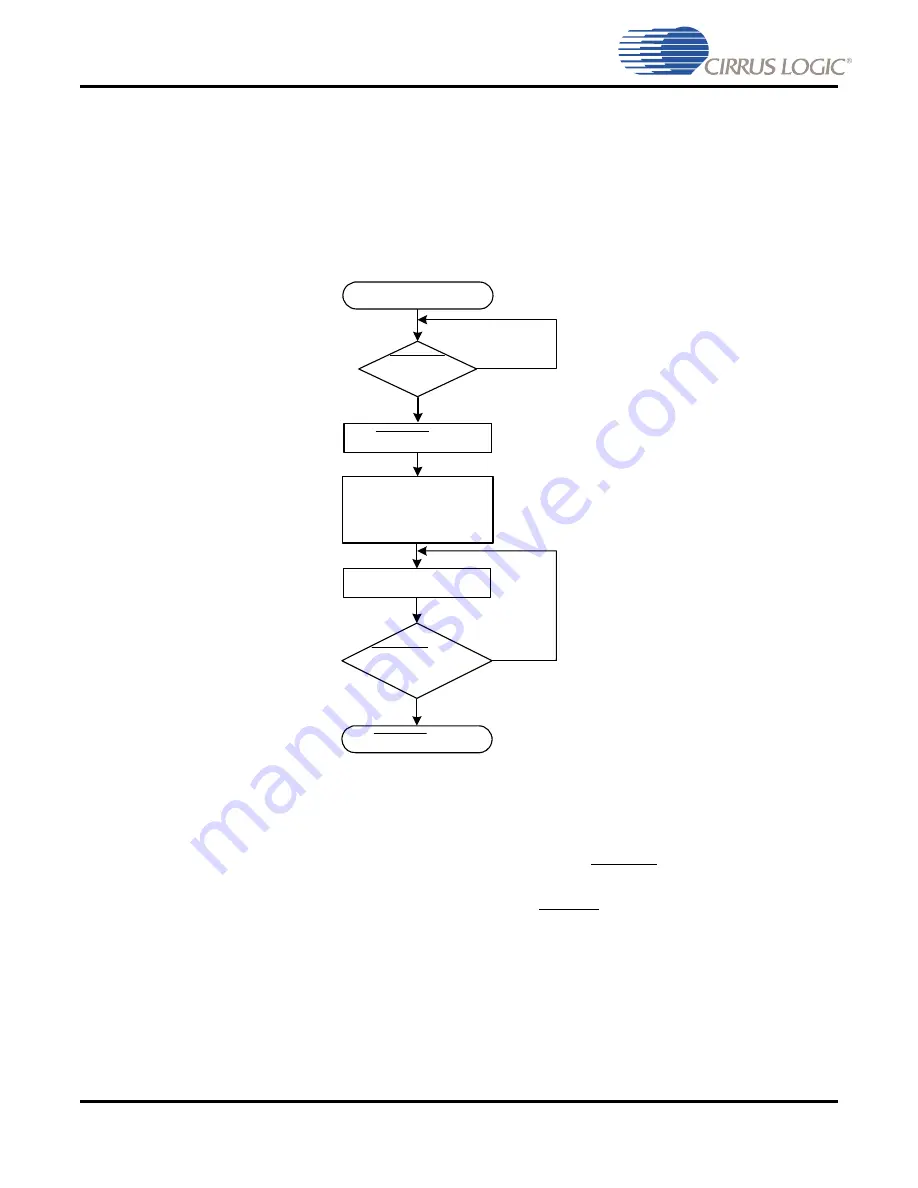

The flow diagram shown in

Figure 3-16

, illustrates the sequence of events that define the SPI read protocol.

This protocol is discussed in the high-level procedure in

Section 3.3.1.4.1

Figure 3-16. SPI Read Flow Diagram

3.3.1.4.1 SPI Read Protocol Procedure

1. A SPI read transaction is initiated by the CS485xx slave driving SCP_IRQ low to indicate that it has

data to be read.

2. The master begins a SPI transaction driving chip select (SCP_CS) low.

3. This is followed by a 7-bit address and the read/write bit set high for a read. So, the master should

send 0x81. The 0x81 byte represents the 7-bit SPI address 1000000b, and the least significant bit set

to ‘1’, designates a read.

4. After the falling edge of the serial control clock (SCP_CLK) for the read/write bit, the master can begin

clocking out the 4-byte word from the CS485xx on the MISO pin. Data clocked out of the CS485xx by

the master is valid on the rising edge of SCP_CLK and data transitions occur on the falling edge of

SCP_CLK. The serial clock should be held low so that eight transitions from low-to-high-to-low will

occur for each byte.

SCP_IRQ

(LOW)?

SCP_IRQ STILL

LOW?

SCP_CS HIGH

Y

N

Y

N

START

SCP_CS LOW

READ 4 DATA BYTES

WRITE ADDRESS BYTE

0x81