Digital Audio Input Port Description

CS485xx Hardware User’s Manual

DS734UM7

Copyright 2009 Cirrus Logic, Inc.

4-2

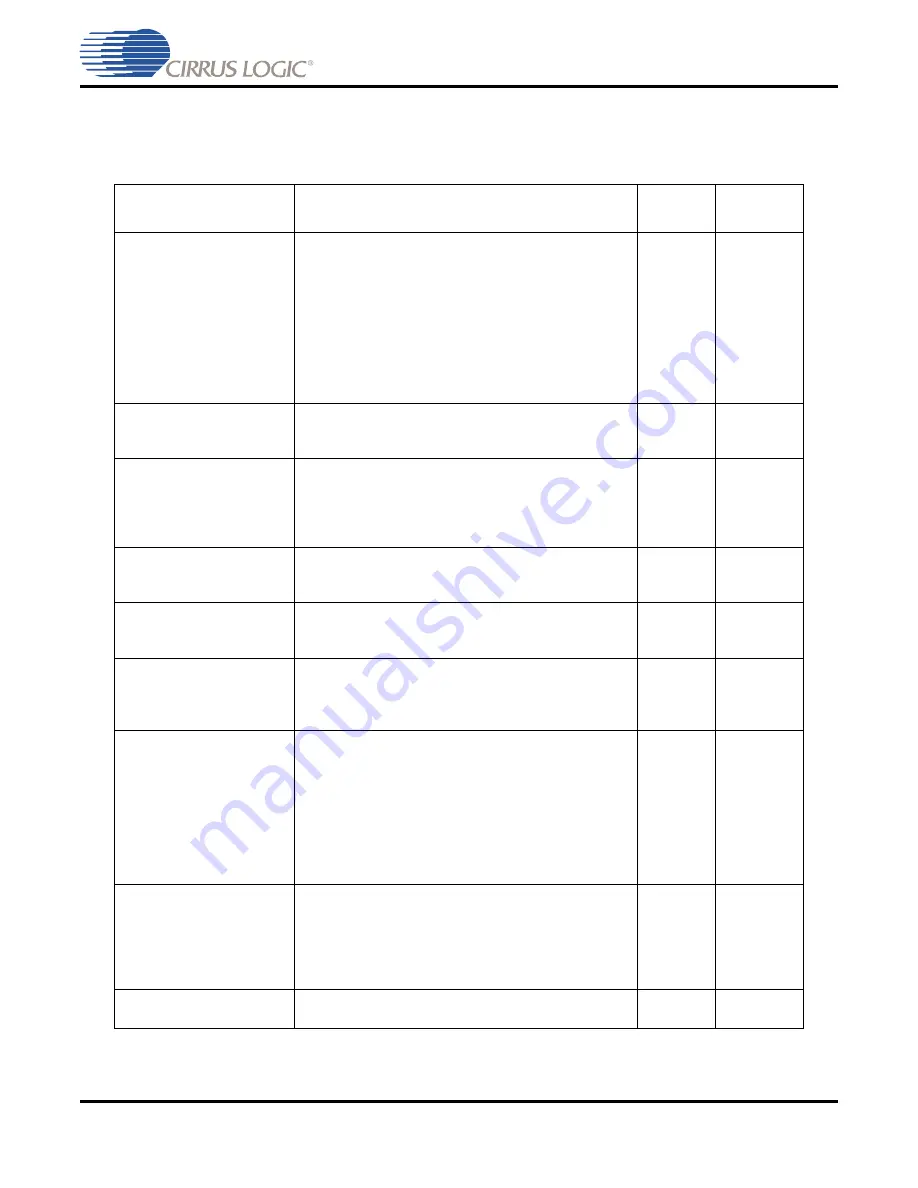

4.2.1 DAI Pin Description

Table 4-1

shows the mnemonic and pin description of the pins associated with the DAI port on CS485xx.

Table 4-1. Digital Audio Input Port

Pin Name

Pin Description

LQFP-48

Pin #

Pin Type

DAI1_LRCLK or

DAI1_DATA5

Sample Rate Clock 1 PCM Audio Input Sample Rate

(LeftRight) Clock

DAI1_LRCLK is the sample rate input clock for the serial

PCM audio data on DAI_DATA[3:0] when in dual-clock

domain mode.

DAI_DATA4 is used for PCM Audio Input Data when

configured for single-clock domain mode.

Note:

DAI1_DATA4 is not available on CS48540

DAI1_DATA4 is not available on CS48520

6

Input

DAI1_SCLK

Bit Clock 1 PCM Audio Input Bit Clock

DAI1_SCLK is the bit clock input for the serial PCM

audio data on DAI_DATA[3:0]..

8

Input

DAI1_DATA0

PCM or Compressed Audio Input Data 0 PCM Audio

Input Data 0

Serial data input that can accept PCM audio data that is

synchronous to DAI_SCLK1/DAI_LRCLK1 or

DAO_SCLK/DAO_LRCLK..

10

Input

DAI1_DATA1

PCM Audio Input Data

Note:

DAI1_DATA1 is not available on CS48520

11

Input

DAI1_DATA2

PCM Audio Input Data

Note:

DAI1_DATA2 is not available on CS48520

13

Input

DAI1_DATA3

PCM Audio Input Data

Note:

DAI1_DATA3is not available on CS48540

DAI1_DATA3 is not available on CS48520

14

Input

DAI2_LRCLK

Sample Rate Clock 2 PCM Audio Input Sample Rate

(LeftRight) Clock

DAI2_LRCLK is the sample rate input clock for the serial

PCM audio data on DAI2_DATA0 in dual-clock domain

mode.

DAI2_LRCLK is the sample rate input clock for seral

PCM audio data on DAI_DATA[5:0] in single-clock

domain mode.

17

Input

DAI2_SCLK

Bit Clock 2 PCM Audio Input Bit Clock

DAI2_SCLK is the bit clock input for the serial PCM

audio data on DAI2_DATA0 in dual-clock domain mode.

DAI2_SCLK is the bit clock input for the serial PCM

audio data on DAI_DATA[5:0] in single-clock domain

mode.

18

Input

DAI2_DATA0 or

DAI1_DATA4

PCM Audio Input Data

15

Input