4-5

Copyright 2009 Cirrus Logic, Inc.

DS734UM7

Digital Audio Input Port Description

CS485xx Hardware User’s Manual

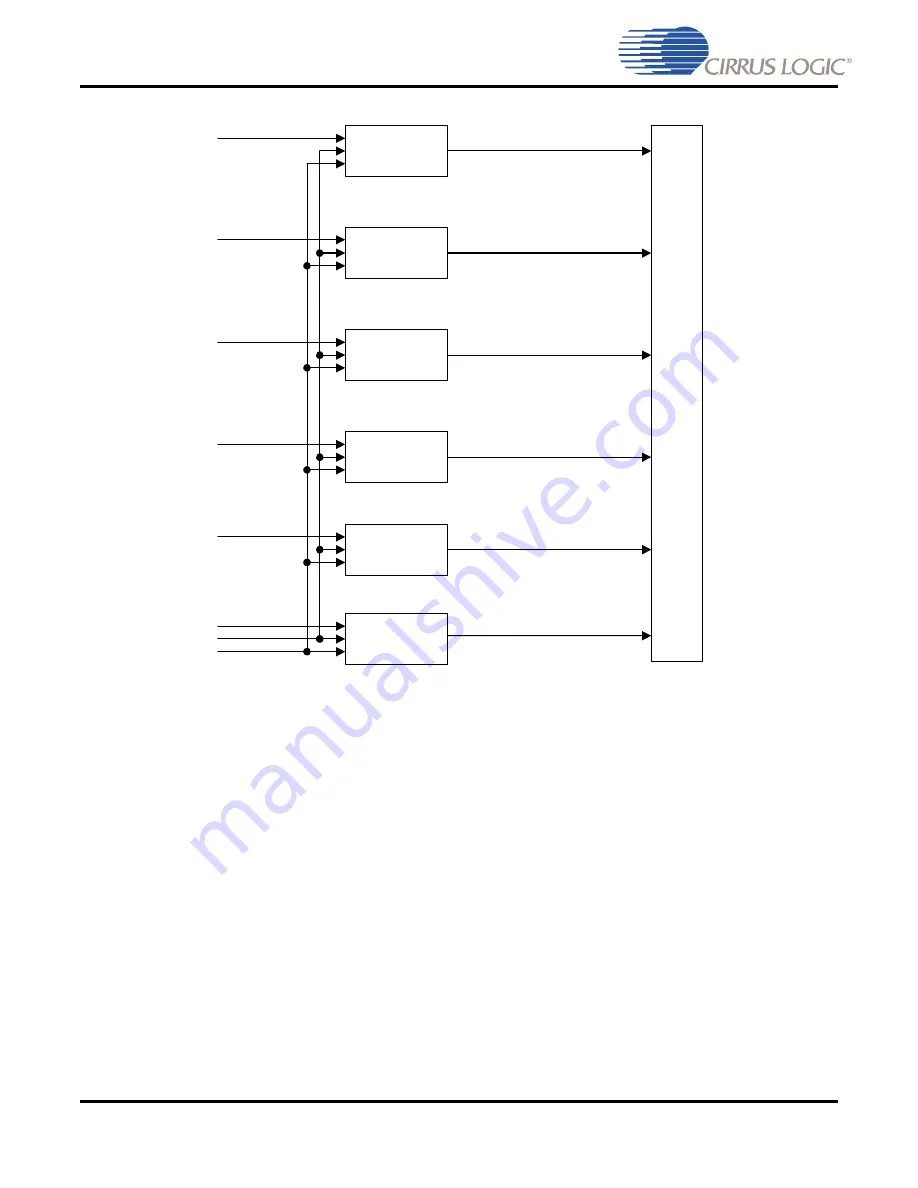

Figure 4-4. 12-Channel DAI Port Block Diagram

4.2.3 Digital Audio Formats

The DAI data input pins are fully configurable including support for I

2

S and left-justified formats. DAI clock

and data pins support only slave operation. This subsection describes some common audio formats that

CS485xx supports. It should be noted that the input ports use up to 32-bit PCM resolution.

4.2.3.1 I

2

S Format

Figure 4-5

illustrates the I

2

S format. For I

2

S, data is presented most-significant bit (MSB) first, one SCLK

delay after the transition of DAIn_LRCLK, and is valid on the rising edge of DAIn_SCLK. For the I

2

S format,

the left subframe is presented when DAIn_LRCLK is low, and the right subframe is presented when

DAIn_LRCLK is high.

DAI1_DATA0

DMA t

o

Pe

ri

p

h

e

ra

l

Bu

s

DAI1_DATA0

DAI1_DATA1

DAI1_DATA1

DAI1_DATA2

DAI1_DATA2

DAI1_DATA3

DAI1_DATA3

DAI1_DATA5

DAI1_DATA5

DAI_LRCLK2

DAI_SCLK2

DAI1_DATA4

DAI1_DATA4