CDB4923 CDB49300

48

DS262DB2

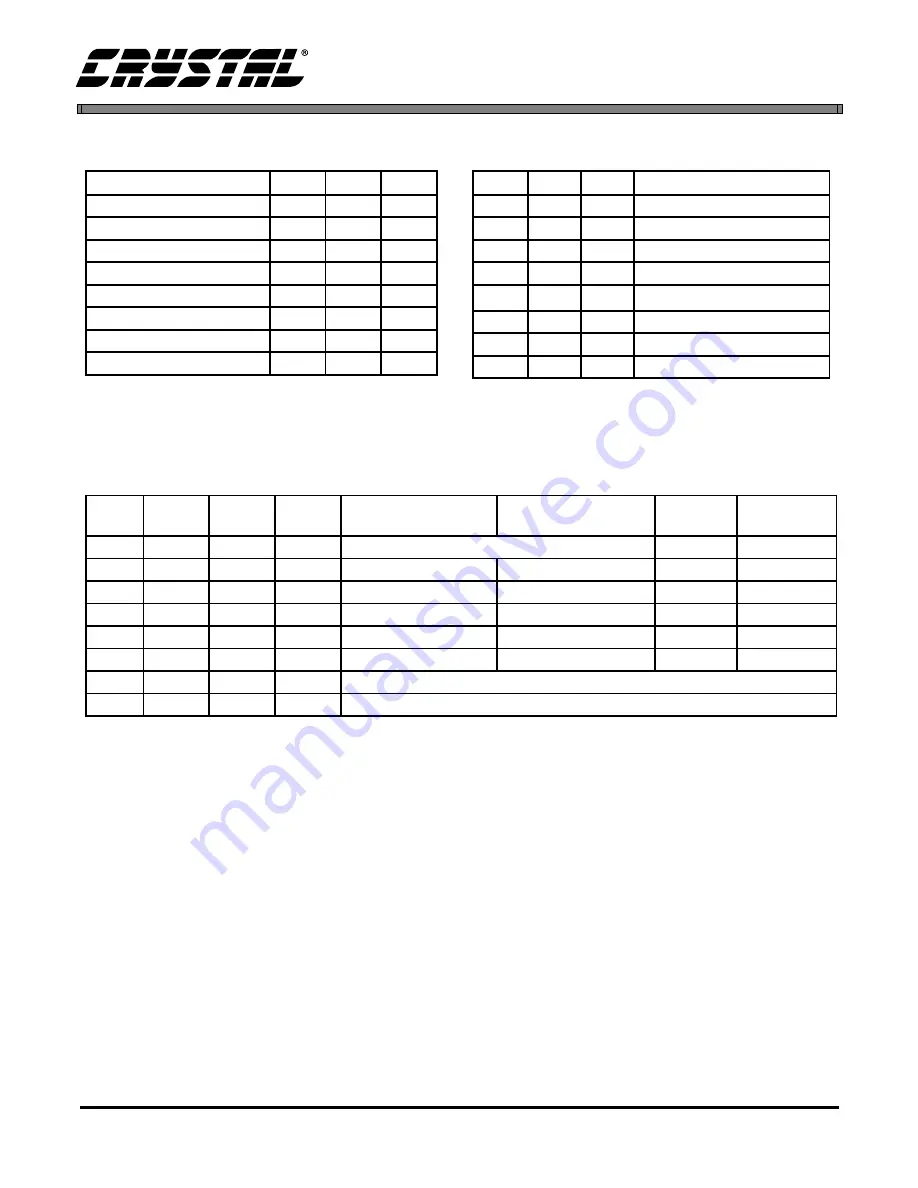

PCLK Frequency

J72

J67

J68

33.33 MHz

LO

LO

LO

54 MHz

LO

LO

HI

66.66 MHz

LO

HI

LO

80 MHz

LO

HI

HI

32 MHz

HI

LO

LO

81 MHz

HI

LO

HI

50 MHz

HI

HI

LO

40 MHz

HI

HI

HI

Table 22. PCLK Configurations

M2

M1

M0

Audio Serial Port Format

LO

LO

LO

FSYNC & SCK Output

LO

LO

HI

Left/Right, 16-24 Bits

LO

HI

LO

Word Sync, 16-24 Bits

LO

HI

HI

Reserved

HI

LO

LO

Left/Right, I

2

S (default)

HI

LO

HI

LSB Justified, 16 Bits

HI

HI

LO

LSB Justified, 18 Bits

HI

HI

HI

MSB Last, 16-24 Bits

Table 23. Digital Input Format settings for CS8404A

(S2)

PLD

Mode

DATA

SEL2

DATA

SEL1

DATA

SEL0

CS492X/CS493XX

CMPDAT

CS492X/CS493XX

SDATAN1

MCLK

MASTER

CONTROL

SOURCE

0

LO

LO

LO

Data and Control lines accessed via J11 and J12

J12 or DSP

J11 & J12

1

LO

LO

HI

S/PDIF -- CS8414

A/D -- CS5334

CS8414

J11 & J12

2

LO

HI

LO

PC

A/D -- CS5334

DSP

PC

3

LO

HI

HI

S/PDIF -- CS8414

S/PDIF -- CS8414

CS8414

PC

4

HI

LO

LO

S/PDIF -- CS8414

A/D -- CS5334

CS8414

PC

5

HI

LO

HI

A/D -- CS5334

A/D -- CS5334

OSC/PLL

PC

6

HI

HI

LO

RESERVED

7

HI

HI

HI

RESERVED

Table 24. Data Selection Modes (Switch S3, PLD Version AB-X)

Summary of Contents for CS492 Series

Page 18: ...CDB4923 CDB49300 18 DS262DB2 9 APPENDIX A SCHEMATICS Figure 4 CS492x CS493xx ...

Page 19: ...CDB4923 CDB49300 DS262DB2 19 Figure 5 System Power ...

Page 20: ...CDB4923 CDB49300 20 DS262DB2 Figure 6 PC Interface ...

Page 21: ...CDB4923 CDB49300 DS262DB2 21 Figure 7 Control Logic ...

Page 22: ...CDB4923 CDB49300 22 DS262DB2 Figure 8 Clocking ...

Page 23: ...CDB4923 CDB49300 DS262DB2 23 Figure 9 Analog Input ...

Page 24: ...CDB4923 CDB49300 24 DS262DB2 Figure 10 Digital Input ...

Page 25: ...CDB4923 CDB49300 DS262DB2 25 Figure 11 D A Converters ...

Page 26: ...CDB4923 CDB49300 26 DS262DB2 Figure 12 Analog Output ...

Page 27: ...CDB4923 CDB49300 DS262DB2 27 Figure 13 Digital Output ...

Page 28: ...CDB4923 CDB49300 28 DS262DB2 Figure 14 Top Layer ...

Page 29: ...CDB4923 CDB49300 DS262DB2 29 Figure 15 Bottom Layer ...

Page 30: ...CDB4923 CDB49300 30 DS262DB2 Figure 16 SSTOP ...

Page 31: ...CDB4923 CDB49300 DS262DB2 31 Figure 17 ASYSTOP ...

Page 32: ...CDB4923 CDB49300 32 DS262DB2 Figure 18 Layer 2 ...

Page 33: ...CDB4923 CDB49300 DS262DB2 33 Figure 19 Layer 3 ...

Page 49: ... Notes ...

Page 50: ......