DS785UM1

4-5

Copyright 2007 Cirrus Logic

Boot ROM

EP93xx User’s Guide

4

4

4

Note: ASYNC boot mode is the preferred boot mode type for new designs.

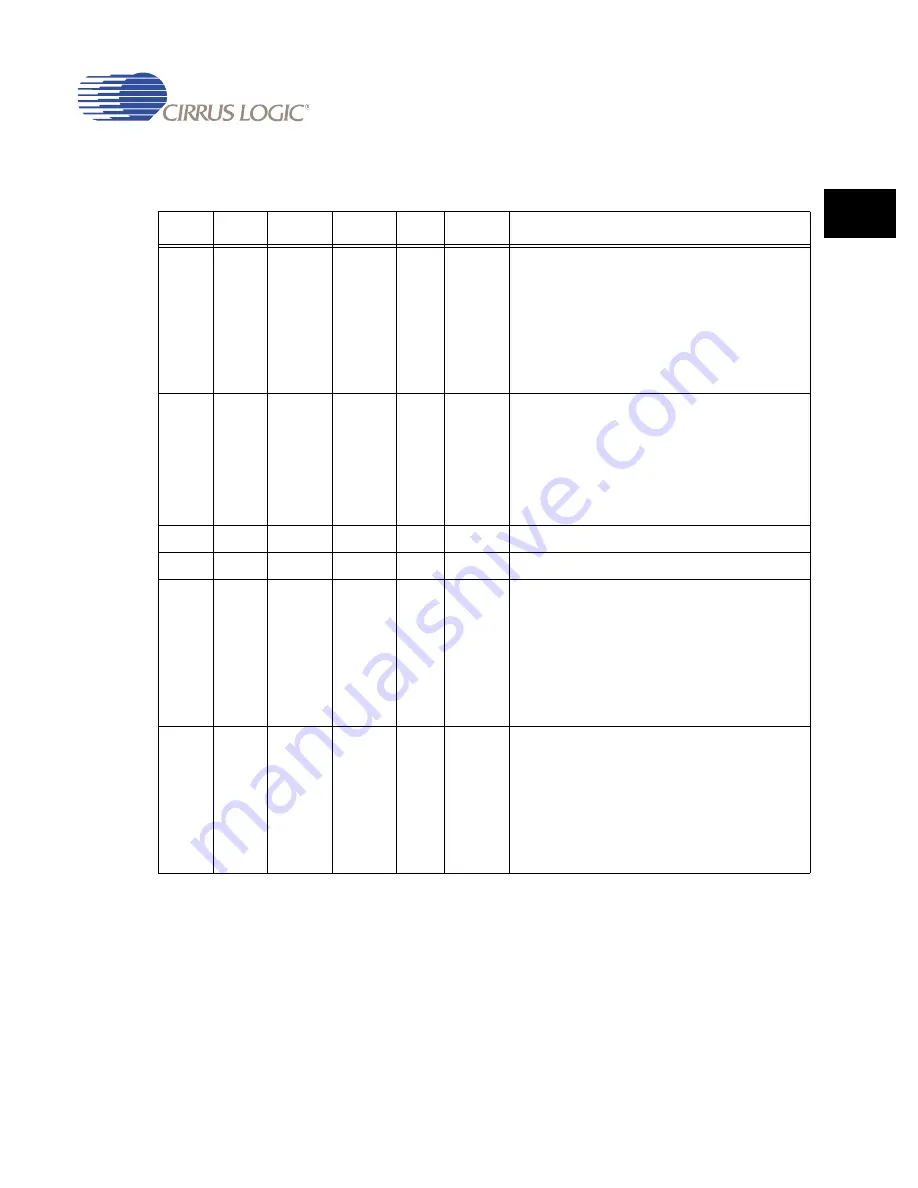

Table 4-1. Boot Configuration Options

EECLK EEDAT

BOOT1

BOOT0

ASDO CSn[7:6]

Boot Configuration

0

1

0

0

1

0 0

0 1

1 0

1 1

External boot using Sync boot mode and SDCSn3.

The media type must be either SyncROM or

SyncFLASH. The selection of the bus width is

determined by latched CSn[7:6] value:

16-bit

16-bit

32-bit

32-bit

0

1

0

0

0

0 0

0 1

1 0

1 1

External boot using Async boot mode and CSn0. The

selection of the bus width is determined by latched

CSn[7:6]

value:

8-bit

16-bit

32-bit

32-bit

1

1

0

1

x

xx

Internal boot from UART1.

1

1

0

0

x

xx

Internal SPI boot if HeaderID is found.

1

1

0

0

1

0 0

0 1

1 0

1 1

Internal boot using SYNC boot mode at the chip select

where the HeaderID exists. The selection of the bus

width is determined by latched CSn[7:6] value:

16-bit

16-bit

32-bit

32-bit

See memory map in

for SYNC

boot mode.

1

1

0

0

0

0 0

0 1

1 0

1 1

Internal boot using ASYNC boot mode at the chip

select where the HeaderID exists. The selection of the

bus width is determined by latched CSn[7:6] value:

8-bit

16-bit

32-bit

32-bit

See memory map in

for

ASYNC boot mode.

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...