DS785UM1

7-65

Copyright 2007 Cirrus Logic

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7

7

7

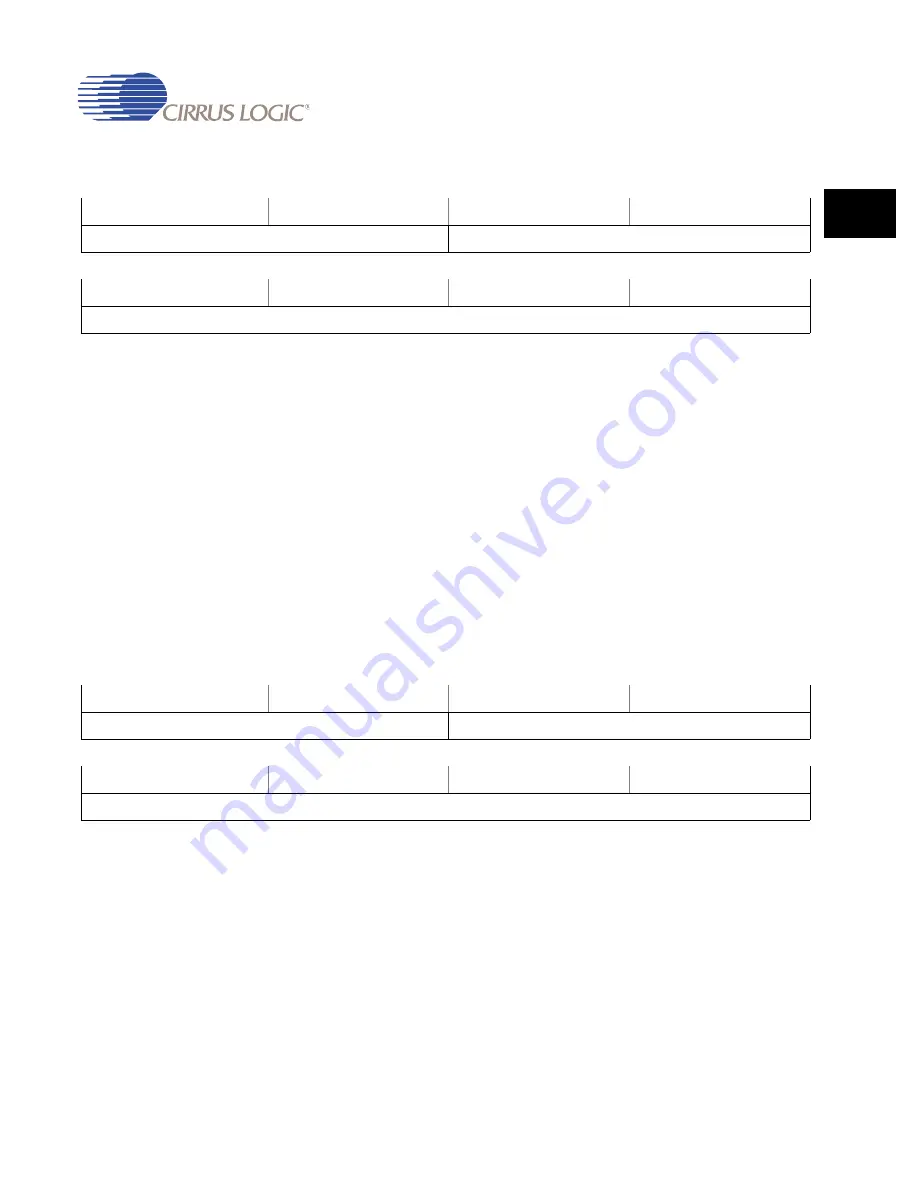

PattrnMask

Address: 0x8003_004C

Default: 0x0000_0000

Definition: Blink Pattern Mask register

Bit Descriptions:

RSVD:

Reserved - Unknown during read

PMASK:

Pattern Mask - Read/Write

The Blink Pattern Mask value that is written to this field

defines which bits of the PATRN field in the

register are used to validate a blink pixel:

0 - Bit used for comparison

1 - Bit not used for comparison

BkgrndOffset

Address: 0x8003_0050

Default: 0x0000_0000

Definition: Blink Background Color / Blink Offset value register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

PMASK

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PMASK

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

BGOFF

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

BGOFF

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...