8-4

DS785UM1

Copyright 2007 Cirrus Logic

Graphics Accelerator

EP93xx User’s Guide

8

8

8

8.3.1 Breshenham Line Draws

Based on Breshenham's algorithm, this is the fastest of the two lines draws. Patterned lines

drawn are aligned to the major axis. Steps made in the major axis are made on a 4095/4096

pixel step per clock basis. This allows the algorithm to complete the line with the amount of

pixel draws in the major axis. Steps in the minor axis are made in sub pixel increments.

Patterned lines drawn in this mode are aligned to the major axis. A pattern up to 16 bits long

repeats on an interval up to 16 bits. This type of patterning is commonly used.

8.3.2 Pixel Step Line Draws

This is a sub-pixel accumulation line draw that will typically take longer to draw than a

Breshenham line draw. The major advantage of the pixel step line draw is that it provides

angularly corrected patterns. This means that the pattern of the line is applied along the line

at the appropriate angle. The number of algorithm iterations is calculated based on the

calculated pixel length of the line (Pythagorean theorem). A pattern up to 16 bits long repeats

on an interval up to 16 bits. In this mode, visual correctness is emphasized over

completeness. For higher definition patterns, details of the pattern may be lost.

Wide lines are not hardware accelerated, but may be generated by stepping and repeating

single pixel width lines.

If speed is critical, horizontal un-patterned lines may be drawn by single pixel deep block fills.

Note:Line drawing in the negative X or Y directions is not supported by the hardware.

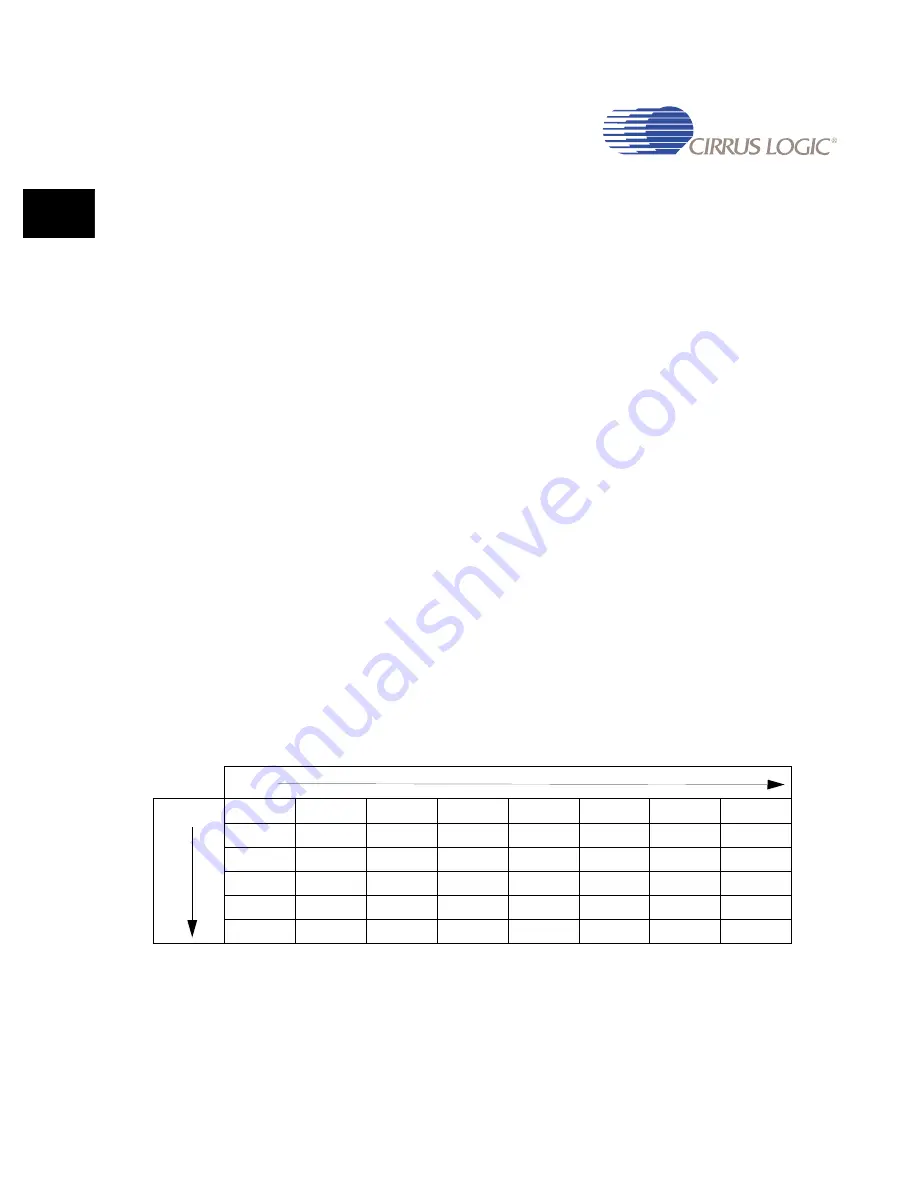

8.4 Memory Organization for Graphics Accelerator

shows a hypothetical 8 x 6 pixel matrix as it would appear on a display.

P(x,y) is defined as a pixel at location x,y from the upper left corner of the screen.

Table 8-1. Screen Pixels

X-Axis

Y-Axis

P(0,0)

P(1,0)

P(2,0)

P(3,0)

P(4,0)

P(5,0)

P(6,0)

P(7,0)

P(0,1)

P(1,1)

P(2,1)

P(3,1)

P(4,1)

P(5,1) P(6,1)

P(7,1)

P(0,2)

P(1,2)

P(2,2)

P(3,2)

P(4,2)

P(5,2)

P(6,2)

P(7,2)

P(0,3)

P(1,3)

P(2,3)

P(3,3)

P(4,3)

P(5,3) P(6,3)

P(7,3)

P(0,4)

P(1,4)

P(2,4)

P(3,4)

P(4,4)

P(5,4)

P(6,4)

P(7,4)

P(0,5)

P(1,5)

P(2,5)

P(3,5)

P(4,5)

P(5,5) P(6,5)

P(7,5)

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...