DS785UM1

8-25

Copyright 2007 Cirrus Logic

Graphics Accelerator

EP93xx User’s Guide

8

8

8

Default:

0x0000_0000

Mask:

0xFFFF_FFFC

Definition:

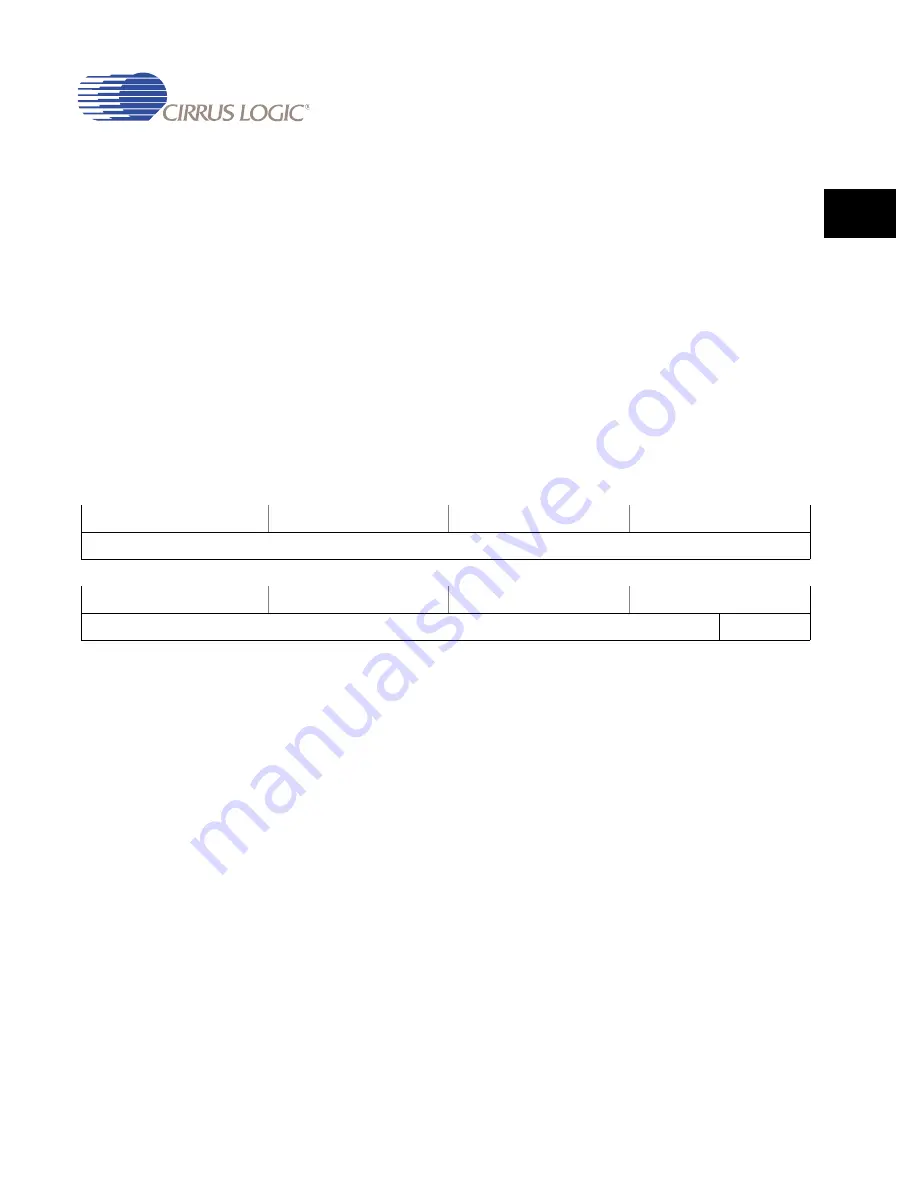

Block Source Word Address Start register

Bit Descriptions:

ADR:

Address - Read/Write

The value in this field specifies the word address of the

SDRAM frame buffer location that contains the starting

pixel (of the first scan line) of the source image.

The ADR field and the PEL field in the

register together define the starting pixel’s address in the

SDRAM frame buffer of the source image.

NA:

Not Assigned - Not used, returns written value

BLKDESTSTRT

Address:

0x8004_000C - Read/Write

Default:

0x0000_0000

Mask:

0xFFFF_FFFC

Definition:

Block Destination Word Address Start register

Bit Descriptions:

ADR:

Address - Read/Write

The value in this field specifies the word address of the

SDRAM frame buffer location that contains the starting

pixel (of the first scan line) of the destination image.

The ADR field and the SPEL field in the

register together define the starting

pixel’s address in the SDRAM frame buffer of the

destination image.

NA:

Not Assigned - Not used, returns written value

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

ADR

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

ADR

NA

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...