9-42

DS785UM1

Copyright 2007 Cirrus Logic

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9

9

9

Chip Reset:

0x0000_0x0x

Rx Reset:

0x0000_0000

Soft Reset:

0x0000_0000

Definition:

Receiver Control Register. The Receive Control register is reset by Rx Reset

signal generated by holding the TESTSELn pin low. The same signal is also

used to reset the receive MAC. The purpose of having a separate reset signal

is to be able to avoid resetting the receive MAC when the AHB bus is in a

powered down state (RESET active), and wake-up frames need to be

detected.

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

Note: The IA field of the table means the same Individual Addresses as RxFCE, that is, IA0

implies RxFCE0 and IA1 implies RxFCE1

PauseA:

Pause Accept. When set, Pause frames are passed on to

the Host as regular frames. When clear, the frames are

discarded. The handling of MAC Control frames depends

on the Pause Accept bit as well as the appropriate

Individual Accept and RxFlow Control Enable bits, as

follows.

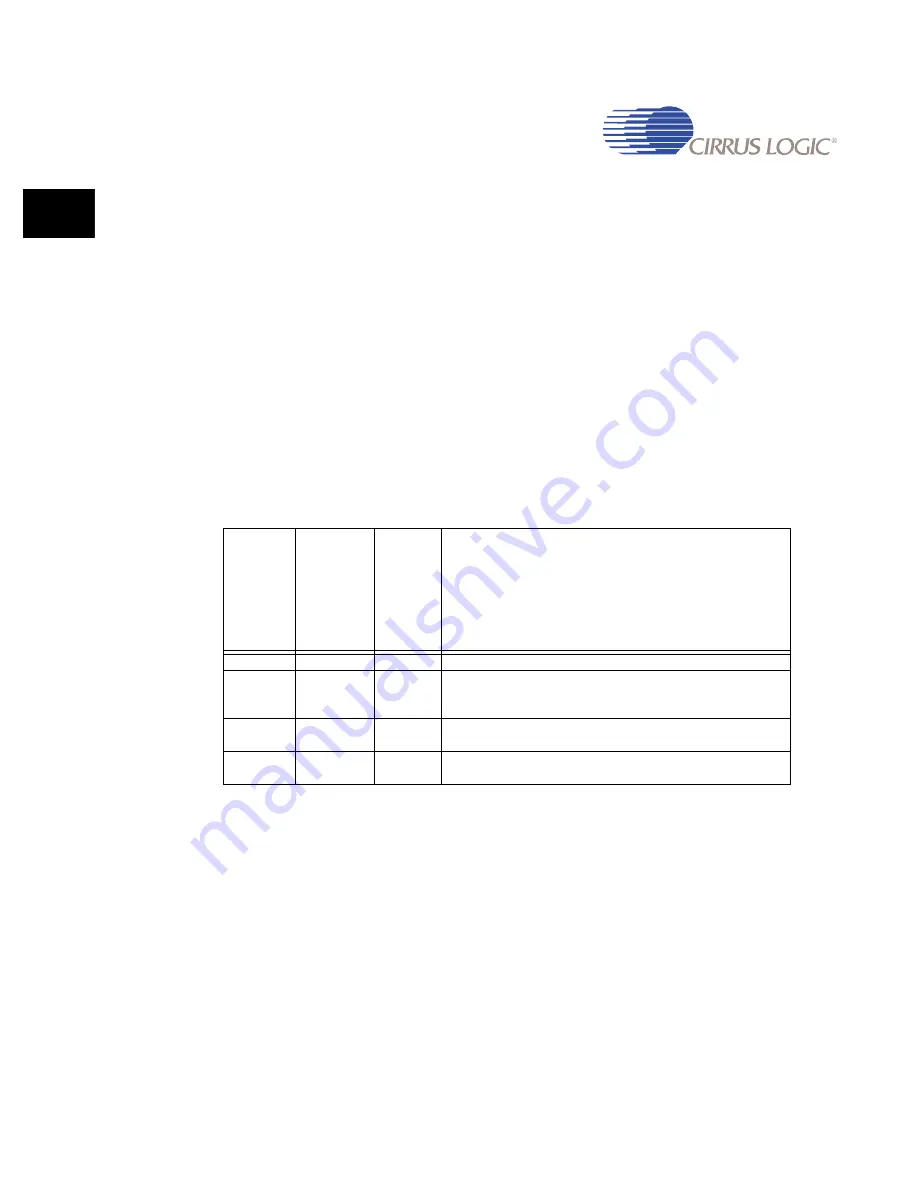

Table 9-4. Individual Accept, RxFlow Control Enable and Pause Accept Bits

IA[1:0]

Individu

al

Accept

RxFCE[1:

0]

Receive

Flow

Control

Enable

PauseA

Pause

Accept

Action

0

X

X

Frame discarded (do not pass the address filter)

1

1

0

MAC Control frames are recognized, flow control action taken,

and frames not passed to host. Non pause MAC Control

frames are passed on to host.

1

1

1

MAC Control frames are recognized, flow control action taken,

and all MAC control frames are passed on to host.

1

0

X

MAC Control frames are not distinguished from other frame

types, all frames passed on to host.

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...