DS785UM1

10-33

Copyright 2007 Cirrus Logic

DMA Controller

EP93xx User’s Guide

1

0

1

0

10

Example: if BWC = 1010b (indicating 1024 bytes, see

, below), the DMA relinquishes control of the

bus on completion of the current burst transfer

after BCR

values which are within 15 bytes of multiples of 1024.

PW:

Peripheral Width. For external DMA transfers, these bits

are used to program the DMA to request byte/half-

word/word wide AHB transfers, depending on the width of

the external device. These bits are not used for software

triggered M2M transfers.

00 - Byte (8 bits)

01 - Half-word (16 bits)

10 - Word (32 bits)

11 - Not used

For word accesses the lower 2 bits of the

source/destination address are ignored.

For half-word accesses the lower bit of the

source/destination address is ignored.

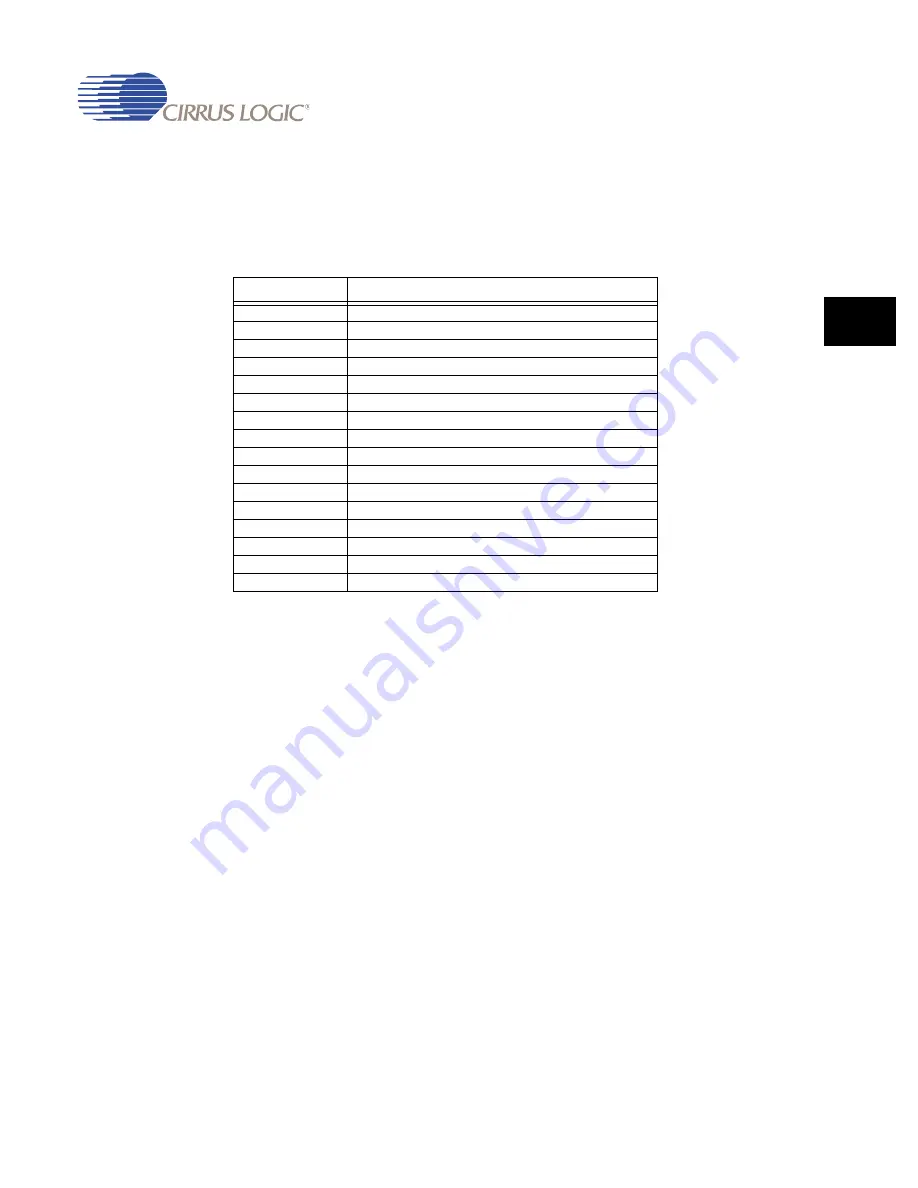

Table 10-9. BWC Decode Values

BWC

Bytes

0000

Full DMA transfer completes

0001

16

0010

16

0011

16

0100

16

0101

32

0110

64

0111

128

1000

256

1001

512

1010

1024

1011

2048

1100

4096

1101

8192

1110

16384

1111

32768

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...