DS785UM1

2-25

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

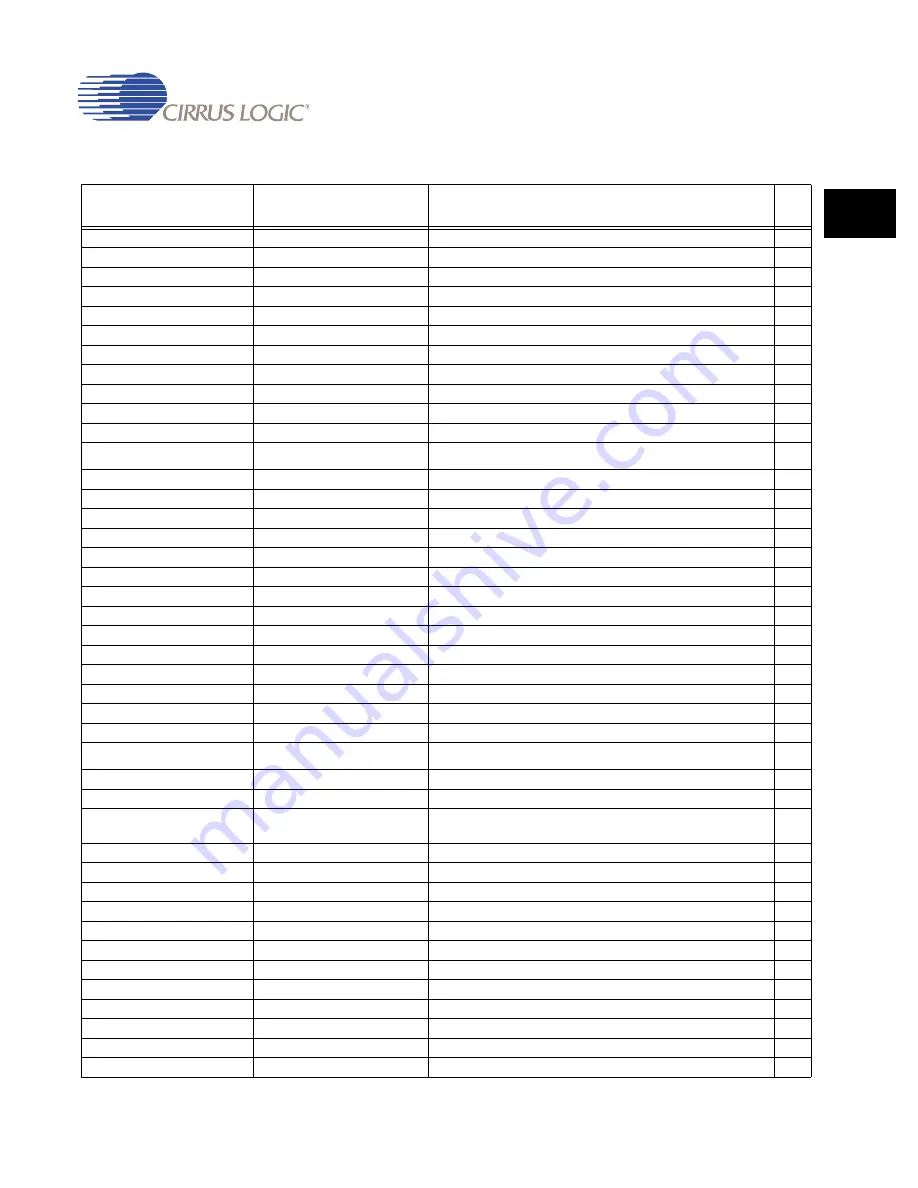

0x800C_022C

VIC2VectCntl11

Vector control 11 Register

N

0x800C_0230

VIC2VectCntl12

Vector control 12 Register

N

0x800C_0234

VIC2VectCntl13

Vector control 13 Register

N

0x800C_0238

VIC2VectCntl14

Vector control 14 Register

N

0x800C_023C

VIC2VectCntl15

Vector control 15 Register

N

0x800C_0FE0

VIC2PeriphID0

VIC Identification Register bits 7:0

N

0x800C_0FE4

VIC2PeriphID1

VIC Identification Register bits 15:8

N

0x800C_0FE8

VIC2PeriphID2

VIC Identification Register bits 23:16

N

0x800C_0FEC

VIC2PeriphID3

VIC Identification Register bits 31:24

N

0x800C_0FF0 - 0x800C_0FFC

Reserved

N

0x8081_xxxx

TIMER

Timer Registers

0x8081_0000

Timer1Load

Contains the initial value of the timer

N

0x8081_0004

Timer1Value

Gives the current value of the timer

N

0x8081_0008

Timer1Control

Provides enable/disable and mode configurations for the timer

N

0x8081_000C

Timer1Clear

Clears an interrupt generated by the timer

N

0x8081_0020

Timer2Load

Contains the initial value of the timer

N

0x8081_0024

Timer2Value

Gives the current value of the timer

N

0x8081_0028

Timer2Control

Provides enable/disable and mode configurations for the timer

N

0x8081_002C

Timer2Clear

Clears an interrupt generated by the timer

N

0x8081_0060 - 0x8081_0064

Reserved

0x8081_0080

Timer3Load

Contains the initial value of the timer

N

0x8081_0084

Timer3Value

Gives the current value of the timer

N

0x8081_0088

Timer3Control

Provides enable/disable and mode configurations for the timer

N

0x8081_008C

Timer3Clear

Clears an interrupt generated by the timer

N

0x8082_xxxx

I2S

I2S Registers

N

0x8082_0000

I2STXClkCfg

Transmitter clock configuration Register

N

0x8082_0004

I2SRXClkCfg

Receiver clock configuration Register

N

0x8082_0008

I2SGlSts

I2S Global Status Register. This reflects the status of the 3 RX

FIFOs and the 3 TX FIFOs

N

0x8082_000C

I2SGlCtrl

I2S Global Control Register

N

0x8082_0010

I2STX0Lft

Left Transmit data Register for channel 0

N

0x8082_0014

I2STX0Rt

Right Transmit data Register for channel 0

N

0x8082_0018

I2STX1Lft

Left Transmit data Register for channel 1

N

0x8082_001C

I2STX1Rt

Right Transmit data Register for channel 1

N

0x8082_0020

I2STX2Lft

Left Transmit data Register for channel 2

N

0x8082_0024

I2STX2Rt

Right Transmit data Register for channel 2

N

0x8082_0028

I2STXLinCtrlData

Transmit Line Control Register

N

0x8082_002C

I2STXCtrl

Transmit Control Register

N

0x8082_0030

I2STXWrdLen

Transmit Word Length

N

0x8082_0034

I2STX0En

TX0 Channel Enable

N

0x8082_0038

I2STX1En

TX1 Channel Enable

N

Table 2-8. Internal Register Map (Continued)

Address

Register Name

Register Description

SW

Lock

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...