21-16

DS785UM1

Copyright 2007 Cirrus Logic

I

2

S Controller

EP93xx User’s Guide

2

1

2

1

21

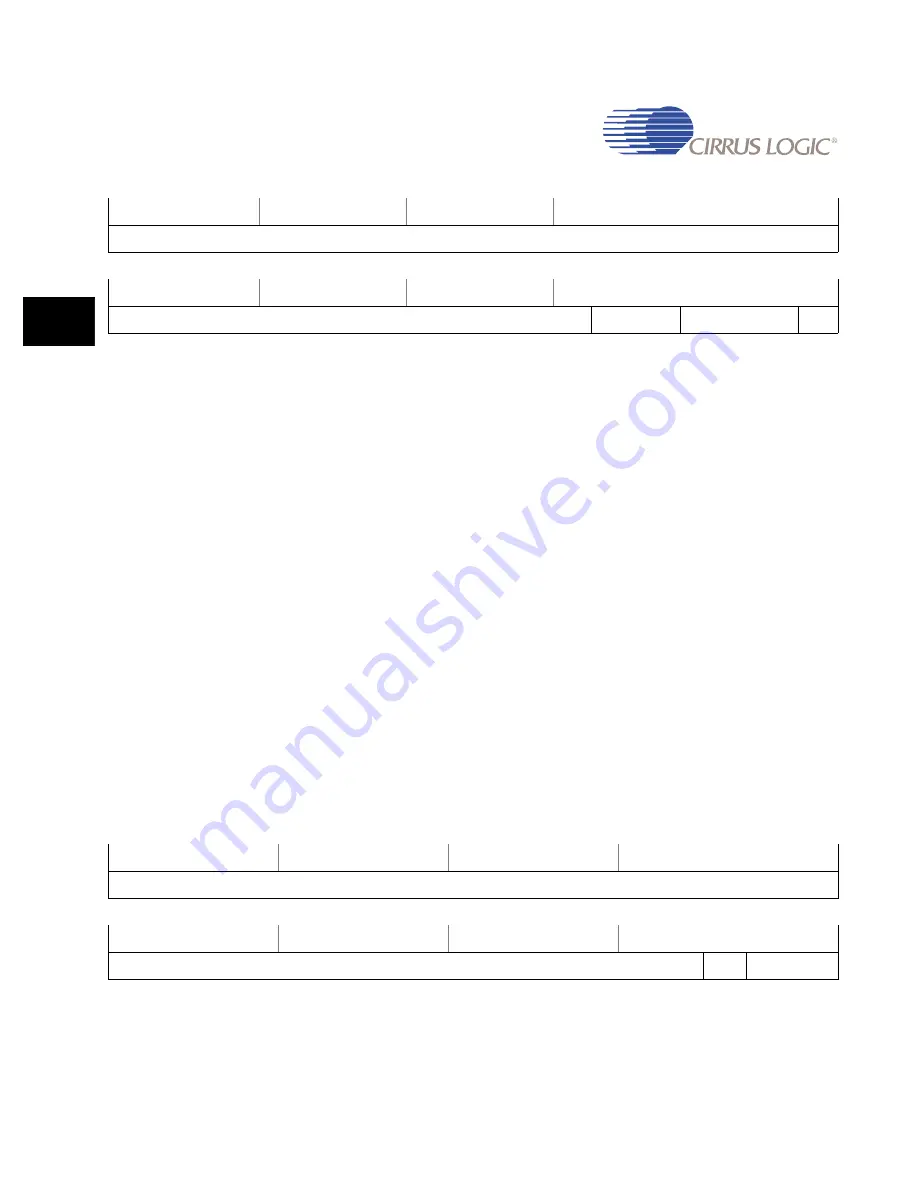

I2STXLinCtrlData

Address:

0x8082_0028 - Read/Write

Default:

0x0000_0000

Definition:

Line Control Data Register

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

Left_Right_Justify: Determines how the data word is justified when being

transmitted on the sdo line output.

0 - left justified.

1 - right justified

TXUF_REPEAT_SAMPLE:On TX underflow, the I

2

S controller transmits all

zeros if this bit is “1”.

If this bit is “0” the I

2

S controller repeats the last sample on

underflow.

TXDIR:

Transmit data shift direction.

0 - MSB first

1 - LSB first

I2STXCtrl

Address:

0x8082_002C - Read/Write

Default:

0x0000_0000

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

Left_Right_Justify

TXUF_REPEAT_SAMPLE

TXDIR

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

TXUFIE

TXEMPTY_int_level

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...