24-6

DS785UM1

Copyright 2007 Cirrus Logic

Pulse Width Modulator

EP93xx User’s Guide

2

4

2

4

24

Default:

0x0000_0000

Definition:

PWMx Invert

Bit Descriptions:

RSVD:

Reserved. Unknown During Read.

INV:

Invert PWM output

0 = Output is not inverted. PWMOUT will output t

ON

first

then t

OFF

, PWMxDutyCycle controls t

ON

1 = Output is inverted. PWMOUT will output t

OFF

first then

t

ON

, PWMxDutyCycle controls t

OFF

.

PWM_INV is double buffered to allow it to be programmed

statically (PWM is stopped) or dynamically (PWM is

running).

Programmed statically, the invert takes affect after the

APB write completes and CLK_PWM is running. After the

update, CLK_PWM can be turned off without affecting

PWMOUT. In this way, the PWM output can be inverted

without enabling the PWM.

Programmed dynamically, PWM_INV is updated at the

end of a PWM cycle to prevent any output glitches or

errors. Read/write accesses to PWM_INV will read/write

its buffer.

provides an example of the effect of the

PWM_INV invert bit.

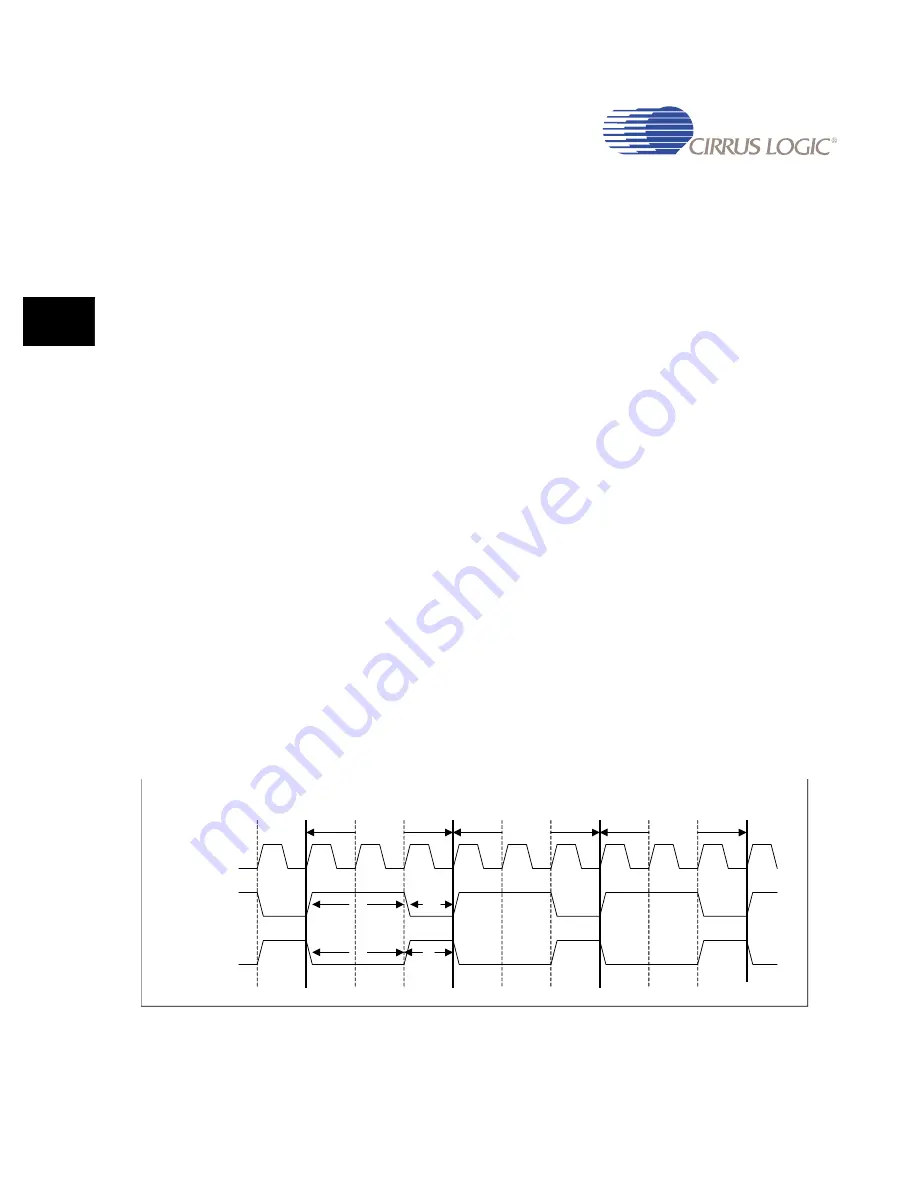

Figure 24-1. PWM_INV Example

clk_pwm

1

2

3

4

5

6

7

8

9

pwmout

PWM_INV = 0

PULSE 1

PULSE 2

PULSE 3

pwmout

PWM_INV = 1

t

on

t

off

t

on

t

off

Duty Cycle =

t

on

/(t

on

+t

off

)

Duty Cycle =

t

off

/(t

on

+t

off

)

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...