DS785UM1

27-7

Copyright 2007 Cirrus Logic

IDE Interface

EP93xx User’s Guide

2

7

2

7

27

latching of the data. It is calculated that the cycle time of AHB clock has to be smaller than

(IDE cycle time)*2/3. For different UDMA speed modes, the minimum AHB clock speeds are

listed below. There is no special speed constraint imposed on the design for PIO and MDMA

modes.

27.2.7 DMA Request Latency

27.2.7.1 DMA Request Deassertion

Multi-word DMA Write to IDE Controller:

The DMAide signal deassertion is generated based on the AHB write logic. The act of writing

to the Multi-word DMA write-FIFO causes the deassertion to appear on the following bus

cycle.

Multi-word DMA Read from IDE Controller:

The DMAide signal deassertion is generated based on the AHB read logic. The act of

reading from the Multi-word DMA read-FIFO causes the deassertion to appear on the

following bus cycle.

Ultra DMA Write to IDE Controller:

The DMAide signal deassertion is generated based on the contents of the Ultra DMA write

FIFO. If the FIFO contains four or more elements, the DMAide signal deasserts.

Ultra DMA Read from IDE Controller:

The DMAide signal deassertion is generated based on an internal counter. The DMAide

signal will deassert if four DMA reads have occurred or if the FIFO is now empty (which only

occurs at the end of a non-quad word aligned read from the IDE device)

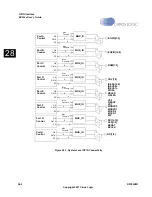

27.2.7.2 DMA Request Latency Overview

The IDE controller requires a certain number of cycles to deassert the DMA request line

DMAide after a DMA access for Multi-word DMA and Ultra DMA modes. The number of wait-

states required are listed below in addition to the pipeline breakdown of the signal

propagation. The assumption is that the deassertion should follow an AHB bus command

(read or write) in HCLK cycle 1.

Table 27-2. IDE Cycle Times and Data Transfer Rates

UDMA Speed Mode

Min. IDE Cycle Time

Max. AHB Cycle

Time

Min. AHB Clock

Frequency

0

112 ns

74.7 ns

13.4 MHz

1

73 ns

48.7 ns

20.5 MHz

2

54 ns

36.0 ns

27.8 MHz

3

39 ns

26.0 ns

38.5 MHz

4

25 ns

16.7 ns

59.8 MHz

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...