DS785UM1

7-81

Copyright 2007 Cirrus Logic

Raster Engine With Analog/LCD Integrated Timing and Interface

EP93xx User’s Guide

7

7

7

The STRT value is the value of the horizontal down

counter at which the HSIGEN signal becomes active

(starts). This indicates the start of the signature calculation

for a horizontal line. HSIGEN is an internal block signal.

The SIG_ENABLE control to the video signature analyzer

is enabled by the logical AND of VSIGEN and HSIGEN.

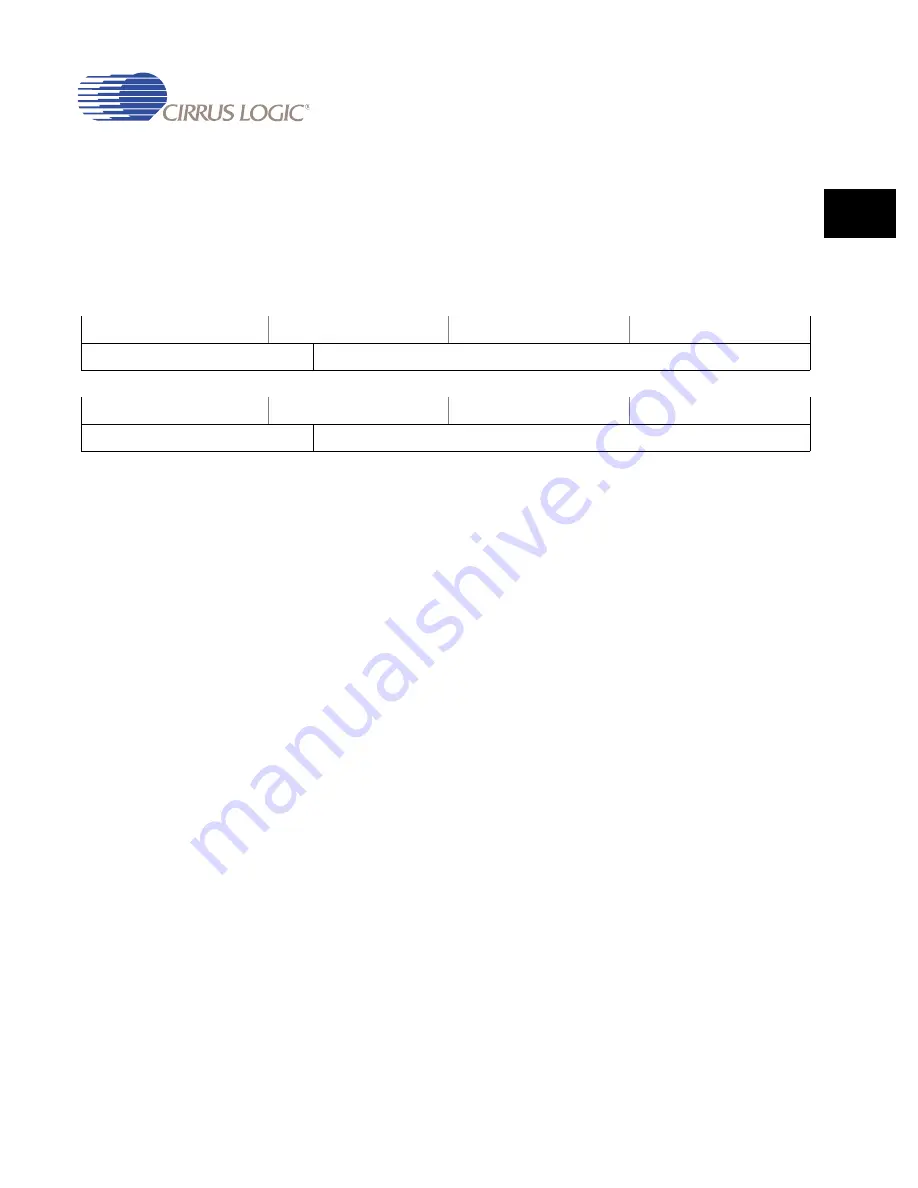

SigClrStr

Address: 0x8003_0210

Default: 0x0000_0000

Definition: Signature Clear and Store Location register

Bit Descriptions:

RSVD:

Reserved. Unknown during read.

VCLR:

Vertical Clear - Read/Write

The VCLR value is the value of the Vertical down counter

at which the VSIGCLR signal is active. This indicates the

line for clearing the LFSR and storing the result value for

the Vertical frame. VSIGCLR is an internal block signal.

The SIG_CLR control to the video signature analyzer is

generated by the logical AND of VSIGCLR and HSIGCLR.

The SigClrStr control signal is also routed to an edge

trigger capable interrupt on the interrupt controller for use

as a programmable secondary raster engine interrupt

output.

HCLR:

Horizontal Clear - Read/Write

The HCLR value is the value of the Vertical down counter

at which the HSIGCLR signal is active. This indicates the

specific horizontal pixel clock for clearing the LFSR and

storing the result value within a horizontal line. HSIGCLR

is an internal block signal. The SIG_CLR control to the

video signature analyzer is generated by the logical AND

of VSIGCLR and HSIGCLR. The SigClrStr control signal is

also routed to an edge trigger capable interrupt on the

interrupt controller for use as a programmable secondary

raster engine interrupt output.

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

RSVD

VCLR

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

RSVD

HCLR

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...