DS785UM1

9-23

Copyright 2007 Cirrus Logic

1/10/100 Mbps Ethernet LAN Controller

EP93xx User’s Guide

9

9

9

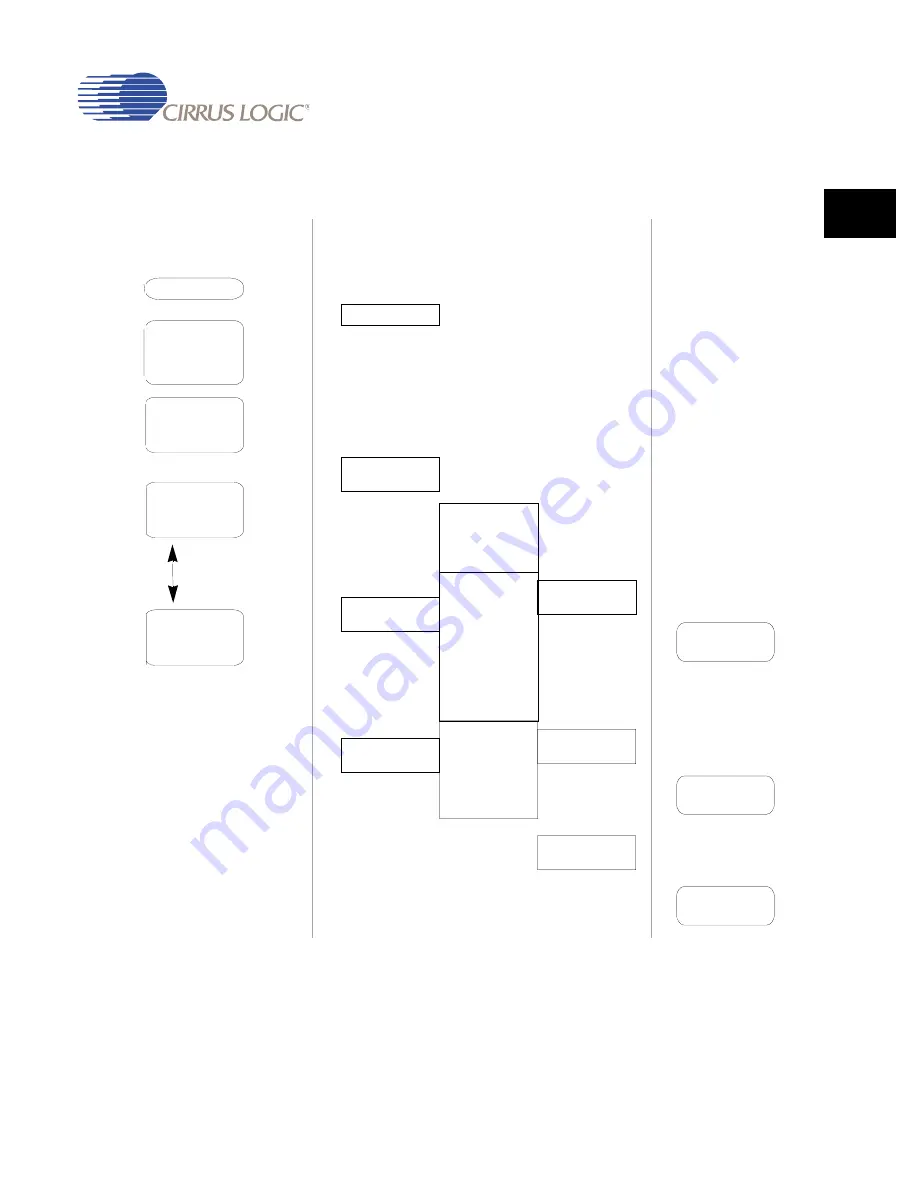

9.2.3.4 Receive Descriptor Data/Status Flow

Figure 9-10. Receive Descriptor Data/Status Flow

SoftWare

HardWare

[ LAN]

SoftWare

Reset

Initialize

Rx Descriptor

and Status

Queues

Write RxDEQ

and RxSEQ

count

Idle

Load

Descriptors

Receive Frame 0

Receive Frame 1

Write RxDEQ

with additional

descriptor count

Random timing between

Write RxDEQ steps

Receive Frame 2

Write

Rx Status

Process Rx Status,

write RxSEQ

Load

Descriptors

Load

Descriptors

Write

Rx Status

Write

Rx Status

Process Rx Status,

write RxSEQ

Process Rx Status,

write RxSEQ

Write RxDEQ

with additional

descriptor count

Pro LAN

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...