2-16

DS785UM1

Copyright 2007 Cirrus Logic

ARM920T Core and Advanced High-Speed Bus (AHB)

EP93xx User’s Guide

2

2

2

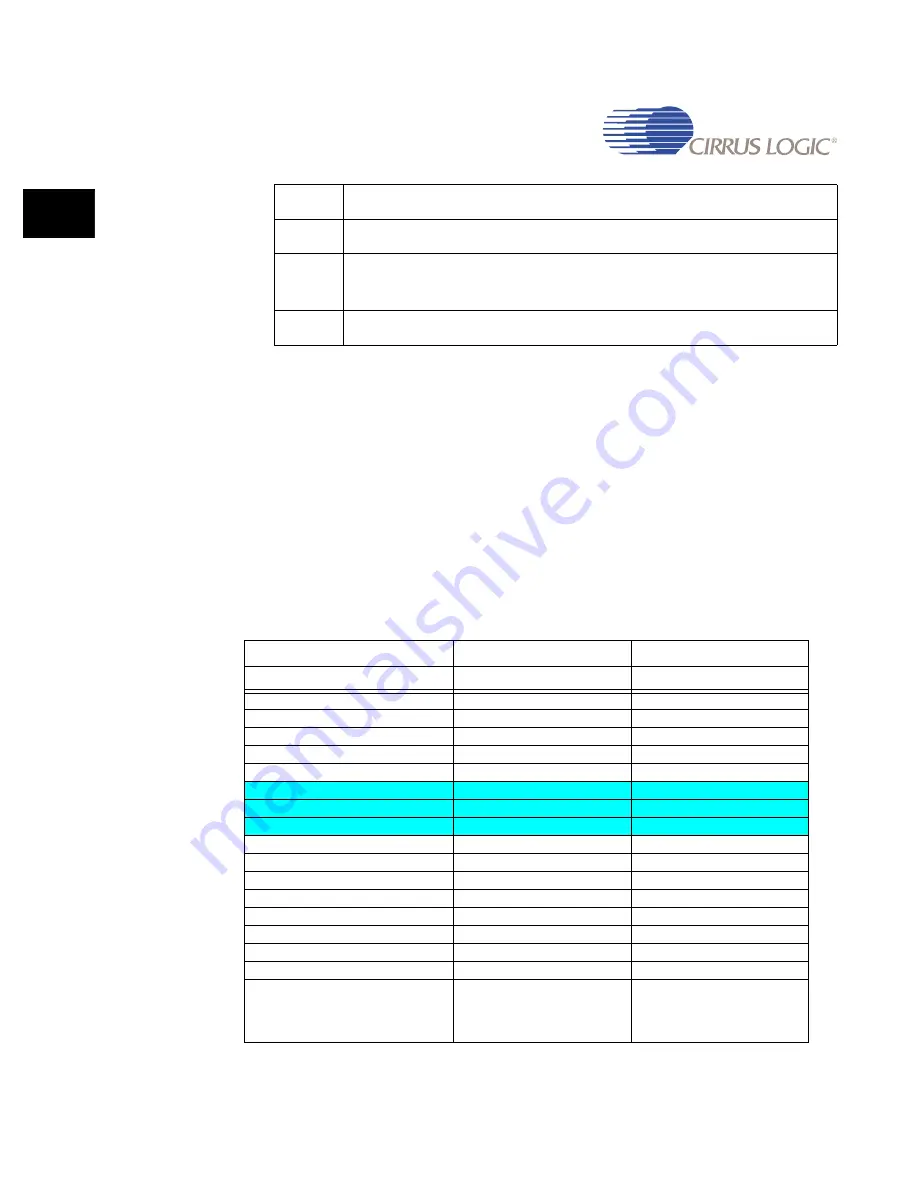

2.3.5 Memory Map

The memory map for Synchronous Memory Boot and Asynchronous Memory Boot is shown

in

.

If internal Boot Mode is selected and the register BootModeClr has been written, the address

range 0x0000_0000 -> 0x0000_FFFF is occupied by the internal Boot ROM until the internal

Boot Code is completed. After boot completion, either Synchronous or Asynchronous

memory is re-mapped to occupy this address space.

NOTE: Some memory locations are listed as Reserved. These memory locations should not

be used. Reading from these memory locations will yield invalid data. Writing to these

memory locations may cause unpredictable results.

11,12,14

Reserved

13

FCSE PID Register:

(Read/Write) ARM9TDMI core addresses ranging from 0 to 32MB are

translated by this register to A + FCSE*32MB and then sent to the MMU. If turned off,

straight addresses are sent to the MMU.

15

Test Register Only:

Reads or writes will cause unpredictable behavior.

Table 2-7. Global Memory Map for the Two Boot Modes

Address Range

Sync Memory Boot

Async Memory Boot

ASD0 Pin = 1

ASD0 Pin = 0

0xF000_0000 - 0xFFFF_FFFF

Async memory (nCS0)

Sync memory (nSDCE3)

0xE000_0000 - 0xEFFF_FFFF

Sync memory (nSDCE2)

Sync memory (nSDCE2)

0xD000_0000 - 0xDFFF_FFFF

Sync memory (nSDCE1)

Sync memory (nSDCE1)

0xC000_0000 - 0xCFFF_FFFF

Sync memory (nSDCE0)

Sync memory (nSDCE0)

0x9000_0000 - 0xBFFF_FFFF

Not Used

Not Used

0x8080_0000 - 0x8FFF_FFFF

APB mapped registers

APB mapped registers

0x8010_0000 - 0x807F_FFFF

Reserved

Reserved

0x8000_0000 - 0x800F_FFFF

AHB mapped registers

AHB mapped registers

0x7000_0000 - 0x7FFF_FFFF

Async memory (nCS7)

Async memory (nCS7)

0x6000_0000 - 0x6FFF_FFFF

Async memory (nCS6)

Async memory (nCS6)

0x5000_0000 - 0x5FFF_FFFF

Reserved

Reserved

0x4000_0000 - 0x4FFF_FFFF

PCMCIA (Slot 0)

PCMCIA (Slot 0)

0x3000_0000 - 0x3FFF_FFFF

Async memory (nCS3)

Async memory (nCS3)

0x2000_0000 - 0x2FFF_FFFF

Async memory (nCS2)

Async memory (nCS2)

0x1000_0000 - 0x1FFF_FFFF

Async memory (nCS1)

Async memory (nCS1)

0x0001_0000 - 0x0FFF_FFFF

Sync memory (nSDCE3)

Async memory (nCS0)

0x0000_0000 - 0x0000_FFFF

Sync memory (nSDCE3)

or

Internal Boot ROM

if INTBOOT is selected

Async memory (nCS0)

or

Internal Boot ROM

if INTBOOT is selected

Table 2-6. CP15 ARM920T Register Description (Continued)

Register

Description

Summary of Contents for EP93 Series

Page 28: ...P 6 DS785UM1 Copyright 2007 Cirrus Logic Preface EP93xx User s Guide PP P ...

Page 162: ...5 36 DS785UM1 Copyright 2007 Cirrus Logic System Controller EP93xx User s Guide 55 5 ...

Page 576: ...15 18 DS785UM1 Copyright 2007 Cirrus Logic UART2 EP93xx User s Guide 1515 15 ...

Page 634: ...17 38 DS785UM1 Copyright 2007 Cirrus Logic IrDA EP93xx User s Guide 1717 17 ...

Page 648: ...19 6 DS785UM1 Copyright 2007 Cirrus Logic Watchdog Timer EP93xx User s Guide 1919 19 ...

Page 688: ...21 32 DS785UM1 Copyright 2007 Cirrus Logic I2S Controller EP93xx User s Guide 2121 21 ...

Page 790: ...27 20 DS785UM1 Copyright 2007 Cirrus Logic IDE Interface EP93xx User s Guide 2727 27 ...

Page 808: ...28 18 DS785UM1 Copyright 2007 Cirrus Logic GPIO Interface EP93xx User s Guide 2828 28 ...