Physical

Description

System

Backplane

The

dual-CyBus

backplane

in

the Cisco

7513

has

an aggregate

bandwidth

of 2.134

gigabits

per

second

Gbps

CyBus

comprises

interface

processor

slots

through

and CyBus

comprises

interface

processor

slots

through

12

Figure

1-6

shows

the orientation

of the

two

CyBuses

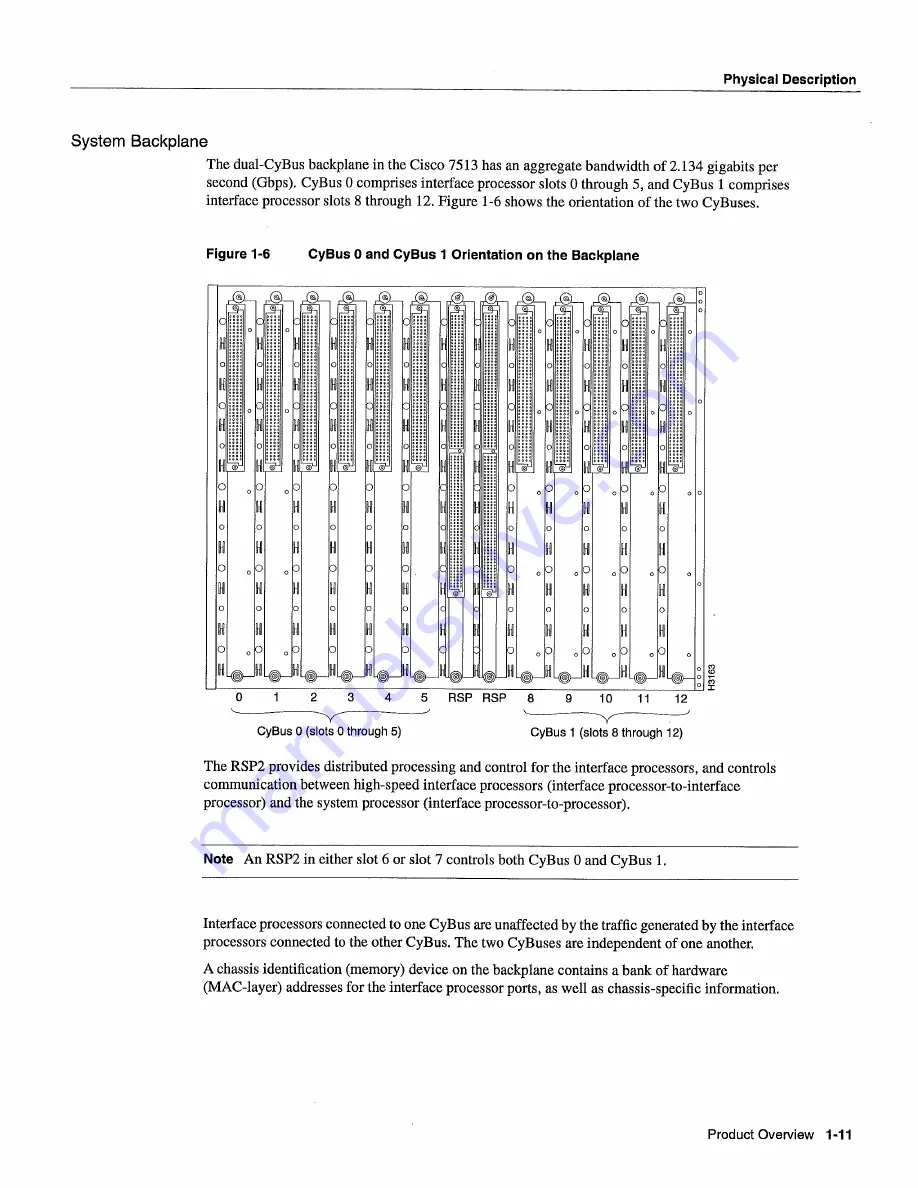

Figure

1-6

CyBus

and

CyBus

Orientation

on

the

Backplane

CyBus

slots

through

The

RSP2

provides

distributed

processing

and

control

for the interface

processors

and

controls

communication

between

high-speed

interface

processors

interface

processor-to-interface

processor and

the system

processor

interface

processor-to-processor

Note

An RSP2

in

either

slot

or

slot

controls

both

CyBus

and

CyBus

Interface

processors

connected

to

one

CyBus

are

unaffected

by

the

traffic

generated

by

the interface

processors

connected

to

the other

CyBus

The

two

CyBuses

are independent

of

one

another

chassis

identification

memory

device

on

the backplane

contains

bank

of

hardware

MAC-layer

addresses

for the interface

processor

ports

as

well

as

chassis-specific

information

RSPRSP

10

11

12

CyBus

slots

through

12

Product

Overview

1-11

Summary of Contents for 7513 Series

Page 1: ......

Page 11: ...Cisco 7513 Hardware Installation and Maintenance ...

Page 121: ...Site Log 2 56 Cisco 7513 Hardware Installation and Maintenance ...

Page 162: ...Troubleshooting the Processor Subsystem 4 10 Cisco 7513 Hardware Installation and Maintenance ...

Page 266: ...Interface Processor LEDs B 16 Cisco 7513 Hardware Installation and Maintenance ...

Page 270: ...C 4 Cisco 7513 Hardware Installation and Maintenance ...

Page 288: ...18 Cisco 7513 Hardware Installation and Maintenance ...