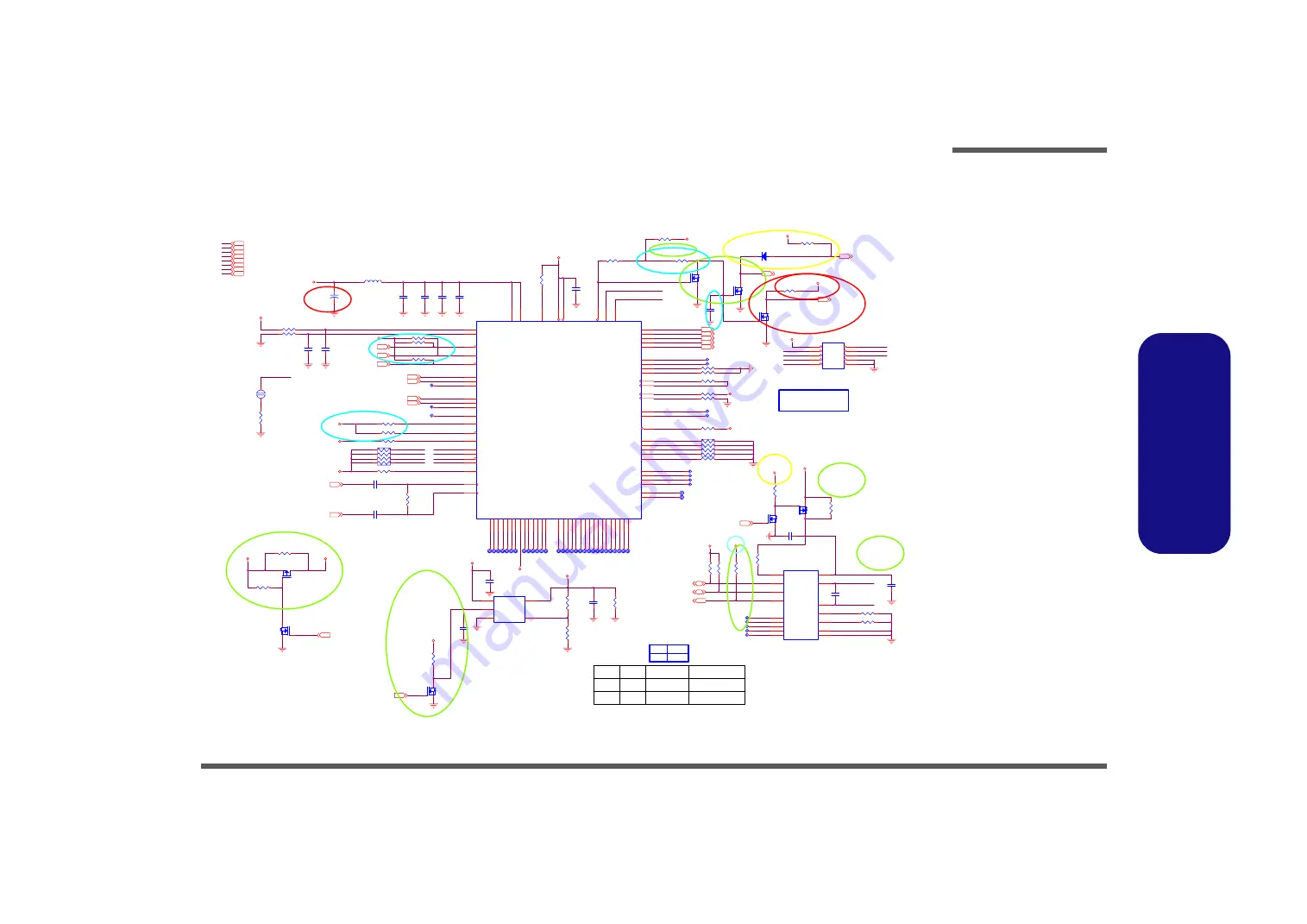

Schematic Diagrams

ATHLON 64 3/4 Misc B - 5

B.Sch

em

atic D

iag

rams

ATHLON 64 3/4 Misc

Sheet 4 of 45

ATHLON 64 3/4

Misc

2.5VDDA

+1.25V

+1.2VLDTB

+2.5V

+3V

2.5VDDA

+2.5V

+2.5V

2.5VDDA

+VDD3

+2.5V

+2.5V

+VDD3

+VDD3

+2.5VS

+12V+

2.5VDDA

+3V

+2.5V

+2.5VS

+2.5V

+3VS

+3VS

CPU_VID4 32

CPU_VID0 32

CPU_VID1 32

CPU_VID2 32

CPU_VID3 32

CPUCLK_H

9

VCORE+

5,32

CPUCLK_L

9

VDDIOFB_H

30

VDDIOFB_L

30

TRMTRIP# 30,34

+3V 9,10,11,13,14,17,18,19,20,21,22,23,24,26,29,32,33

+3VS 2,8,9,10,11,12,13,14,16,18,19,22,23,24,25,28,29,32,33,35,36

+2.5V 3,5,6,7,16,30,33

+1.25V 3,7,30

+1.2VLDTB 2

H8-THERMTRIP# 22

VCORE 5,32

CPU_PWRGD

9

THERMAL_SCLK1

22,36

THERMAL_SDA1

22,36

CPU_ALERT#

13

THERMER_RST

22

+12V 8,20,21,23,26,28,29,30,32

+VDD3 8,13,16,19,23,29,30,31

LDTSTOP#

9

CPURST#

9

SUSB#

13,22,24,29,31,36

SUSC# 13,22,30

VCORE-

5,32

THERMTRIP# 9

CPU_VID4

CPU_VID3

CPU_VID2

CPU_VID1

CPU_VID0

Z0413

Z0412

Z0410

BP3

BP2

Z0414

Z0415

Z0405

P_DBRDY

P_TDO

BP0

BP1

P_DBREQ_L

Z0406

Z0427

Z0404

SCANCLK1

SCANEN

SCANCLK2

DCLKTWO

Z0403

Z0417

Z0416

Z0420

Z0

4

2

6

L0_REF0

Z0401

L0_REF1

Z0402

Z0411

Z0418

Z0419

SCANSHENB

SCANSHENA

Z0428

Z0430

CPURST#

THERMDC

THERMDA

Z0408

Z0425

Z0423

THERMDA

THERMDC

Z0422

Z0409

Z0424

Z0421

Z0429

Z0434

Z0432

Z0433

Z0407

P_TCK

P_TMS

P_TDI

P_TRST_L

P_TRST_L

P_TDI

P_TCK

P_TMS

EN_2.5VDDA

Z0431

P_TMS

P_TDO

P_TDI

P_TCK

P_DBRDY

P_TRST_L

P_DBREQ_L

Z0435

Z0436

Z0

4

66

Z0

46

5

Z0

4

6

4

Z0

46

3

Z0

4

60

Z0

46

2

Z0

4

6

1

Z0

4

59

Z0

45

1

Z0

45

2

Z0

4

5

4

Z0

45

6

Z0

45

8

Z0

4

5

7

Z0

45

5

Z0

45

3

Z0

4

4

5

Z0

44

6

Z0

4

5

0

Z0

44

4

Z0

4

4

3

Z0

4

4

9

Z0

44

8

Z0

44

7

Z0

4

3

9

Z0

44

2

Z0

44

1

Z0

43

8

Z0

44

0

Z0

43

7

R819

680

T664

T6

94

T6

9

5

T665

T6

9

0

T6

89

T6

93

T6

9

2

T6

8

5

T6

80

T6

8

8

T6

9

1

T6

84

T6

87

T6

83

T6

86

T6

8

1

T6

82

T6

7

3

T6

78

T6

77

T6

74

T6

72

T6

75

T6

7

6

T6

79

T6

71

T6

69

T6

6

7

T6

68

T6

7

0

T6

66

T23

R186

100

C912

0.22U

R172

680

R196

680

T24

R109

*11.5K_1%

Q49

NDS352

G

D

S

R146

44.2_1%

ATHLON 64 (C)

U36C

ZIF_SOCKET754

AH

2

5

AJ

2

5

AF20

AE18

AJ27

AF27

AE26

A23

A24

B23

AE12

AF12

AE11

AJ21

AH21

AJ23

AH23

AE24

AF24

C1

6

AG1

5

AH17

C15

E20

E17

B21

A21

C18

A19

AJ28

A28

AF21

AF22

AF23

AE23

C1

J3

R3 AA

2

D3

AG

2

B1

8

AH

1

AE

2

1

C2

0

AG4

C6

AG6

AE

9

AG9

A2

0

A2

6

A2

7

AE15

AF15

AG14

AF14

AG13

AG17

AG18

AH18

AJ18

AH19

AJ19

AE19

D18

C19

D20

C21

B19

A22

AF

1

8

D2

2

C2

2

B1

3

B7

C3

K1

R2

AA

3

F3

C2

3

AG

7

AE

2

2

C2

4

A2

5

C9

AE

1

3

VD

D

A

1

VD

D

A

2

RESET_L

PWROK

LDTSTOP_L

L0_REF1

L0_REF0

COREFB_H

COREFB_L

CORE_SENSE

VDDIOFB_H

VDDIOFB_L

VDDIO_SENSE

CLKIN_H

CLKIN_L

NC_AJ23

NC_AH23

NC_AE24

NC_AF24

VT

T

_

A

5

VT

T

_

B

5

DBRDY

NC_C15

TMS

TCK

TRST_L

TDI

NC_C18

NC_A19

KEY0

KEY1

NC_AF21

NC_AF22

NC_AF23

NC_AE23

NC_

C

1

NC_

J

3

NC_

R

3

N

C

_AA2

NC_

D

3

NC_

A

G

2

NC

_B1

8

NC_

A

H1

NC_

A

E

2

1

N

C

_C

20

NC_

A

G

4

NC

_

C

6

NC_

A

G

6

N

C

_AE9

NC

_

A

G

9

TH

E

R

MTR

IP

_L

TH

E

R

M

D

A

TH

ER

M

D

C

VID0

VID1

VID2

VID3

VID4

NC_AG17

NC_AG18

NC_AH18

NC_AJ18

G_FBCLKOUT_H

G_FBCLKOUT_L

DBREQ_L

NC_D18

NC_C19

NC_D20

NC_C21

NC_B19

TDO

NC_

A

F

1

8

NC

_

D

2

2

NC_

C

2

2

NC_

B

1

3

NC_

B

7

NC_

C

3

NC_

K

1

NC_

R

2

N

C

_AA3

NC_

F

3

NC_

C

23

NC_

A

G

7

NC

__

A

E

2

2

NC_

C

24

NC_

A

25

NC_

C

9

V

TT_

S

E

N

S

E

R713

2.2K

R182

10K

R202

680

T36

R180

680

T27

CA26

*0.1U

R197

0

R101

1K

U6

SC1563ISK

5

2

1

4

3

VIN

GND

SHDN

VO

ADJ

J3

OPEN_1A

1

2

R176

169_1%

R178

820

T33

U7

NE1617

1

5

15

9

13

2

16

12

3

14

4

11

10

6

7

8

N/C1

N/C2

STBY#

N/C3

N/C4

VCC

N/C5

SMBDATA DXP

SMBCLK

DXN

ALERT#

ADD0

ADD1

GND1

GND2

T22

T28

T30

T35

R181

100K

Q40

2N7002

G

D

S

Q26

*2N7002

G

D

S

JDEBUG1

HEADER 10B_R

1

2

3

4

5

6

7

8

9

10

C83

2200P

C117

1000P

CA28

3300P

R105

2.2K

R323

*0_0805

T32

R97

1K

R204

80.6

R203

*560

T34

R523

*0

R148

*100K

C79

0.1U

C144

3900P_0805

R183

*560

R173

*560

C90

0.1U

Q27

*AO3401

G

D

S

T25

R103

2.2K

CA27

0.22U

Q85

2N7002

G

D

S

R112

100K

R322

100K

R179

680

CT1

4.7U_0805

Q39

2N7002

G

D

S

Q98

2N7002

G

D

S

R145

44.2_1%

R512

820

R110

0

+

C570

100U_10V_7343

1

2

C150

3900P_0805

T31

C673

0.1U

R144

680

Q50

2N7002

G

D

S

R716

0

C116

1000P

R210

680

T29

T37

CA1

0.22U

L19

FCI2520-R33K

T26

CA29

0.1U

R187

680

R717

10K

RN35

8P4RX560_0402

1

2

3

4

5

6

7

8

R98

*470_0805

R184

680

RN34

8P4RX560_0402

1

2

3

4

5

6

7

8

C82

*0.1U

D28

1N4148

A

C

Rout with 10/5/10

or differential

pairs 5/5/5/5/5

Low active to short

down system.

+2.5V 2.4~2.6 35mA

S1 ON S3 OFF

EN_2.5VDDA--> Low: Enable Hi :Disable

300nH/350mA

TOP SIDE

12 mil

VCORE Feedback

DUAL2.5V,DUAL1.25V Feedback

The cpu core is held in Low pow er state & MRMCLKA/B & MEMRESET_L

Output are forced Low , When CPURST# IS Asserted.

35mA

35mA

Hyper Transport I/O Compensation

R35 Should be placed as close to the CPU as possible.

G_FBCLKOUT_H

/_L route 8/5/20.

2005/04/20

Adds a +2.5VS voltage source.

5 / 2 0 C h a n g e

5 / 2 0 C h a n g e

5 / 2 0 C h a n g e

D E L + 3 V S

5 / 2 0 C h a n g e

A D D R 7 1 3 ( 2 . 2 K ) .

A D D R 7 1 7 ( 1 0 K ) .

A D D Q 8 5 ( 2 N 7 0 0 2 ) .

A D D R 7 1 6 ( 0 o h m ) .

5 / 2 0 C h a n g e

Q 3 9 , Q 4 0 ( 3 9 0 4 ) C h a n g e 2 N 7 0 0 2 .

5 / 2 0 C h a n g e

D E L R 3 2 4 ( 0 o h m ) .

94/7/25

Del R182, D28, Q40

Rubband

94/7/25

+12V change to +12V +

Rubband

VGA_Slave

ADD0

ADD1

NC

NC

GND

VCC

Address

0101 001

0101 011

VGA_Master

CPU

ID

00

94/9/15

CK8 Therm al Trip

protect

Rubband

94/9/26

Rubband

94/11/11

94/10/31 Kevin

94/10/31 Kevin

94/11/11 Kevin

94/10/31 Kevin

94/10/31 Kevin

680 Change 100K