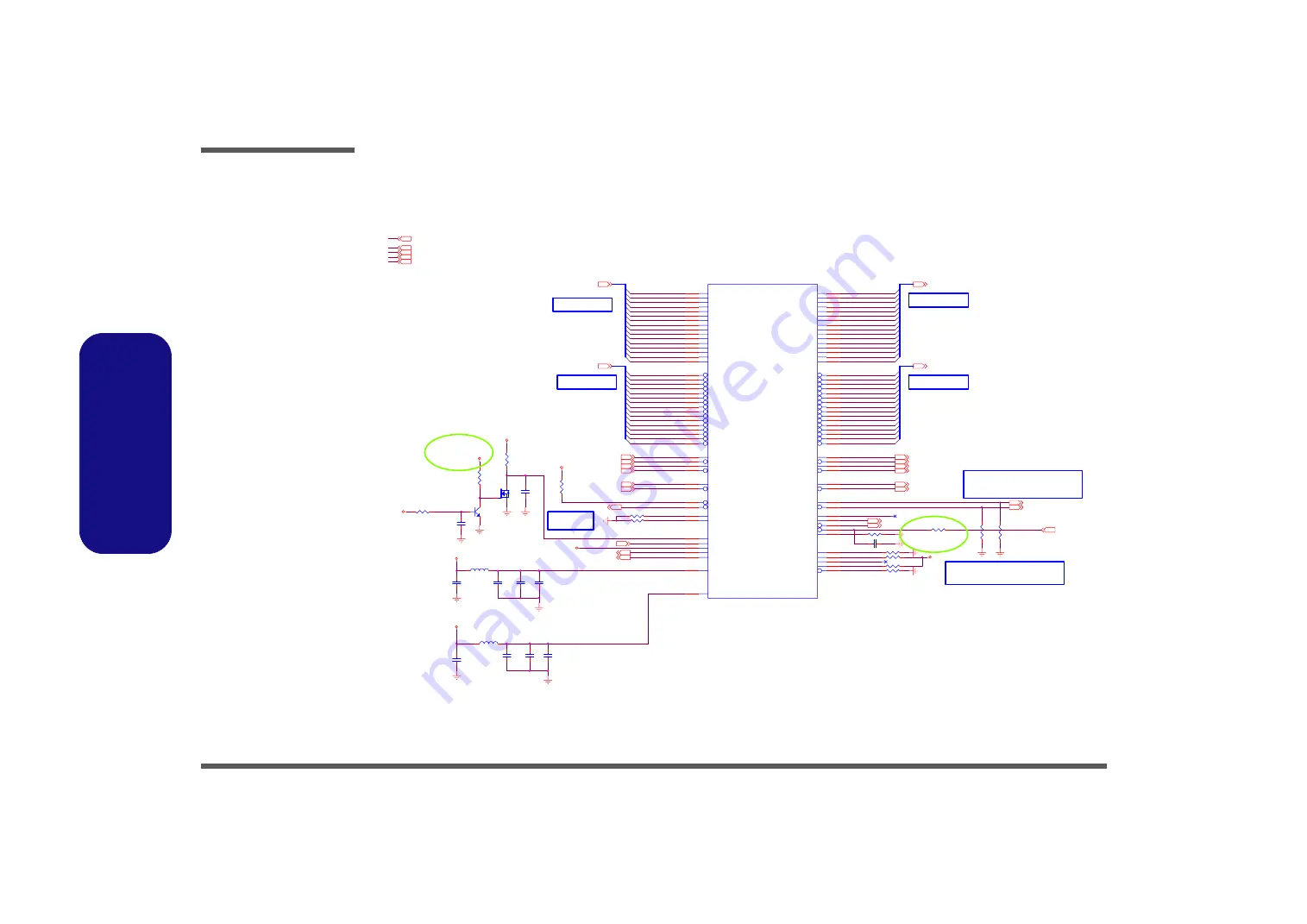

Schematic Diagrams

B - 10 CK804 HT Part A

B.Schematic Diagrams

CK804 HT Part A

Sheet 9 of 45

CK804 HT Part A

+3VS

+3VS

+VDD5

+3V

+3VS

+3VS

+1.2V_HT

+2.5VS

VR_PWRGD

32

HTVDD_EN

2

CPUVDD_EN

32

CPUCLK_H 4

CPUCLK_L 4

THERMTRIP# 4

CPU_PWRGD 4

CPURST# 4

+1.2V_HT 2,14

+3V 4,10,11,13,14,17,18,19,20,21,22,23,24,26,29,32,33

+2.5V 3,4,5,6,7,16,30,33

+3VS 2,4,8,10,11,12,13,14,16,18,19,22,23,24,25,28,29,32,33,35,36

L0_CTLIN_H0 2

L0_CTLIN_L0 2

L0_CLKIN_H1 2

L0_CLKIN_L0 2

L0_CLKIN_L1 2

L0_CLKIN_H0 2

L0_CADIN_L[15..0] 2

L0_CADIN_H[15..0] 2

L0_CADOUT_H[15..0]

2

L0_CADOUT_L[15..0]

2

L0_CLKOUT_H0

2

L0_CLKOUT_L0

2

L0_CLKOUT_H1

2

L0_CLKOUT_L1

2

L0_CTLOUT_H0

2

L0_CTLOUT_L0

2

+VDD5 13,16,19,23,26,29,30,32,34,36

LDTSTOP#

4

HT_COMP2

CK8_TMS

CPUCLK_H

HT_COMP1

CK8_TDO

CPUCLK_L

Z0902

CK8_TDI

TP_CPU_CLK_66

CK8_TCK

CPUVDD_EN

3.3V_PLL_HT

CK8_TRST*

HTVDD_EN

3.3V_PLL_CPU

HT_REQ*

HT_BASE

HT_VLD

Z0903

Z0901

L0_CADOUT_H1

L0_CADOUT_H8

L0_CADOUT_H14

L0_CADOUT_H11

L0_CADOUT_H15

L0_CADOUT_H5

L0_CADOUT_H4

L0_CADOUT_H0

L0_CADOUT_H6

L0_CADOUT_H9

L0_CADOUT_H2

L0_CADOUT_H10

L0_CADOUT_H12

L0_CADOUT_H7

L0_CADOUT_H3

L0_CADOUT_H13

L0_CADIN_H1

L0_CADIN_H5

L0_CADIN_H11

L0_CADIN_H8

L0_CADIN_H12

L0_CADIN_H2

L0_CADIN_H6

L0_CADIN_H14

L0_CADIN_H9

L0_CADIN_H3

L0_CADIN_H10

L0_CADIN_H13

L0_CADIN_H4

L0_CADIN_H7

L0_CADIN_H0

L0_CADIN_H15

L0_CADOUT_L8

L0_CADOUT_L9

L0_CADOUT_L4

L0_CADOUT_L10

L0_CADOUT_L6

L0_CADOUT_L5

L0_CADOUT_L2

L0_CADOUT_L7

L0_CADOUT_L3

L0_CADOUT_L12

L0_CADOUT_L15

L0_CADOUT_L1

L0_CADOUT_L13

L0_CADOUT_L14

L0_CADOUT_L0

L0_CADOUT_L11

L0_CADIN_L8

L0_CADIN_L3

L0_CADIN_L14

L0_CADIN_L6

L0_CADIN_L1

L0_CADIN_L0

L0_CADIN_L15

L0_CADIN_L12

L0_CADIN_L2

L0_CADIN_L13

L0_CADIN_L5

L0_CADIN_L11

L0_CADIN_L4

L0_CADIN_L10

L0_CADIN_L7

L0_CADIN_L9

L0_CLKIN_H0

L0_CLKIN_L1

L0_CTLIN_L0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CTLIN_H0

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_H0

L0_CLKOUT_L0

L24

L_0603(129)

1

2

SEC 1 OF 7

U4H1A

I101

MBGA740

CK804

AG27

AG28

AD3

AE3

AK4

AJ4

AK5

AF28

AF27

N22

M22

W27

Y28

AB23

AB24

AC28

AC27

Y25

Y23

AA22

AB25

AC25

AD24

AD25

AF26

AA27

AA29

AB29

AB28

AD28

AE28

AF29

AG29

Y26

Y24

Y22

AB26

AC26

AC24

AD26

AE26

AA28

AA30

AB30

AC29

AD27

AE29

AF30

AG30

AC5

AC3

AB6

AC6

AD5

M25

AF25

M28

M26

L27

L29

L28

W28

W29

T24

T23

R27

R28

V23

V25

U26

T22

T26

P23

N26

P24

V28

V30

U29

U27

R29

P30

N30

N28

V22

V24

V26

U22

T25

P22

P26

P25

V29

U30

U28

T28

P28

P29

N29

N27

+3.3V_PLL_CPU

+3.3V_PLL_HT

CPUVDD_EN

HTVDD_EN

MEM_VLD

CPU_VLD

HT_VLD

HT_CAL_GND2

HT_CAL_GND1

HT_STOP*

HT_REQ*

HT_RXCTL*

HT_RXCTL

HT_RX_CLK1*

HT_RX_CLK1

HT_RX_CLK0*

HT_RX_CLK0

HT_RXD15*

HT_RXD14*

HT_RXD13*

HT_RXD12*

HT_RXD11*

HT_RXD10*

HT_RXD9*

HT_RXD8*

HT_RXD7*

HT_RXD6*

HT_RXD5*

HT_RXD4*

HT_RXD3*

HT_RXD2*

HT_RXD1*

HT_RXD0*

HT_RXD15

HT_RXD14

HT_RXD13

HT_RXD12

HT_RXD11

HT_RXD10

HT_RXD9

HT_RXD8

HT_RXD7

HT_RXD6

HT_RXD5

HT_RXD4

HT_RXD3

HT_RXD2

HT_RXD1

HT_RXD0

TRST*

TMS

TDO

TDI

TCK

CPU_COMP

THERMTRIP/GPIO*

CPU_RST*

CPU_PWROK

CPU_CLK_66

CPU_CLK*

CPU_CLK

HT_TXCTL*

HT_TXCTL

HT_TX_CLK1*

HT_TX_CLK1

HT_TX_CLK0*

HT_TX_CLK0

HT_TXD15*

HT_TXD14*

HT_TXD13*

HT_TXD12*

HT_TXD11*

HT_TXD10*

HT_TXD9*

HT_TXD8*

HT_TXD7*

HT_TXD6*

HT_TXD5*

HT_TXD4*

HT_TXD3*

HT_TXD2*

HT_TXD1*

HT_TXD0*

HT_TXD15

HT_TXD14

HT_TXD13

HT_TXD12

HT_TXD11

HT_TXD10

HT_TXD9

HT_TXD8

HT_TXD7

HT_TXD6

HT_TXD5

HT_TXD4

HT_TXD3

HT_TXD2

HT_TXD1

HT_TXD0

R248

10K

R534

10K

C173

0.33U

R206

0

L23

L_0603(129)

1

2

R213

10K

R289

549_1%

C154

0.1U

C153

0.1U

R228

49.9_1%

R229

150_1%

R249

10K

PQ18

2N3904

B

E

C

C822

220P

R295

10K

Q44

2N7002

G

D

S

C580

10U_1206

R558

*200

C581

10U_1206

R561

*200

C163

0.1U

C584

0.1U

R216

6.2K

R200

10K

R195

10K

C164

0.1U

C583

0.1U

C158

*0.1U

BACKUP TERM (NOT REQUIRED)

CK804 Max Power

dissipation 13.5W

Thermal operating

temperature 90C

7mA

10mA

CPU_PWRGD,CPURST# Route 5/10,

Length 1.5"~~7".

CPUCLK_H,CPUCLK_L Route

5/5/20, Match w ithin 75mils of each

other.Length 1.5"~~12".

LDTSTOP#

route 5/10

HT Bus route 5/5

HT Bus route 5/5

HT Bus route 5/5

HT Bus route 5/5

R 2 0 6 ( 1 5 0 ) C h a n g e 0 o h m .

5 / 2 0 C h a n g e

5 / 2 0 C h a n g e