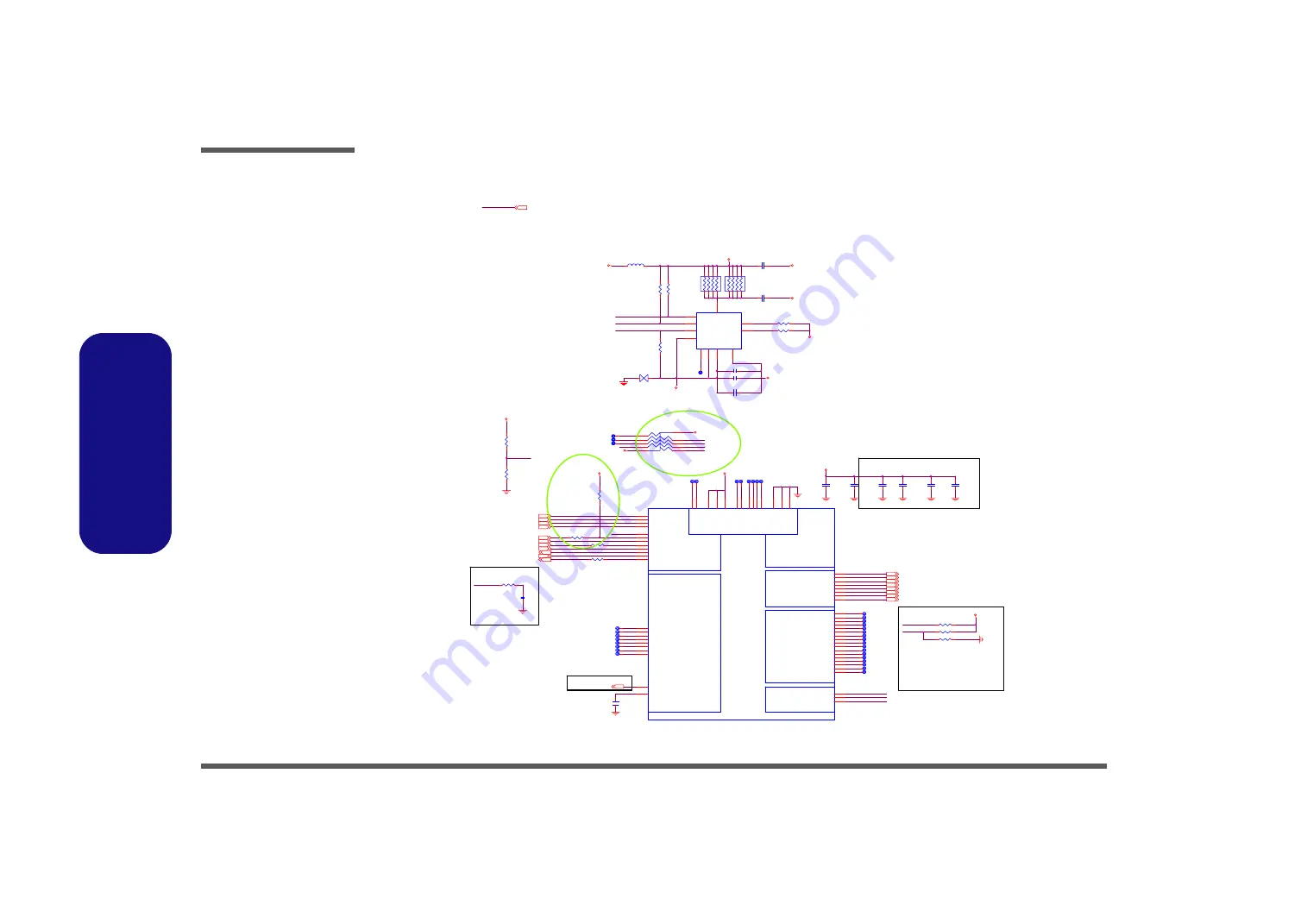

Schematic Diagrams

B - 26 SUPER I/O & FIR

B.Schematic Diagrams

SUPER I/O & FIR

Sheet 26 of 45

SUPER I/O & FIR

+3VS

+3VS

+3VS

FIRGND

FIR GND

+3VS

FIRVCC

FIR GND

FIRGND

FIRVC C

GND

+3VS

+3VS

+3VS

+3VS

LPC_AD2

11,22,23

LPC_DRQ#0

11

PCLK_IO

11

INT_SERIRQ

11,20,22

LPC_AD1

11,22,23

LPC_FRAME#

11,22,23

BUF_SIO_CLK

13

LPC_AD3

11,22,23

LPC_AD0

11,22,23

+3VS 2,4,8,9,10,11,12,13,14,16,18,19,22,23,24,28,29,32,33,35,36

DCDA# 16

SINA 16

DSR A# 16

RTSA# 16

RIA# 16

DTRA# 16

SOU TA 16

CTSA# 16

PCIRST8#

11

D_STEP_CPU

32

SUS_ST#

11

PCLK_IO

R TSA#

IR TX

Z2509

D TRA#

IR RX

IR MODE

Z2510

C LKRU N#

393-48M

+3VS

IRT X

Z

250

7

Z2504

Z2506

IRM O D E

Z2505

IRRX

CLKRUN#

Z2508

Z2511

Z2502

Z2501

LPC_DRQ#0

LPC_AD1

LPC_AD0

LPC_AD3

Z2503

LPC_AD2

Z2512

Z2513

Z2514

Z2515

Z2517

Z2516

Z2519

Z2518

Z2535

Z2533

Z2529

Z2528

Z2531

Z2530

Z2532

Z2534

Z2543

Z2538

Z2542

Z2536

Z2539

Z2537

Z2540

Z2541

Z2544

Z2

52

7

Z2

52

6

Z2

52

4

Z2

52

5

Z2

52

2

Z2

52

3

Z

252

1

Z

252

0

RN1

8P4RX18

1

8

2

7

3

6

4

5

R62

0

R44

0

R39

*10K

T

T

JA1

SHOR T-A

1

2

R 58

*4.7K

R55

2.2K

RP6

10P8RX8.2K

1

2

3

4

5

10

6

7

8

9

RN 2

8P4RX18

1

8

2

7

3

6

4

5

C61

0.047U

T469

T467

L14

L_0805(159)

T465

T477

T473

T475

C56

1000P

T479

T471

T461

T462

T464

T472

R48

47K

T470

T468

C60

0.1U

T463

T466

R38

10K

T480

T478

T484

T482

T483

T474

T481

T476

T4

6

0

R52

2.2K

T485

T4

5

5

T4

5

8

T4

5

7

T4

5

9

R 734

10K

T4

5

4

C63

4.7U_0805

T4

5

3

T4

5

6

0603

C58

0.1U

R56

*4.7K

U3

HSDL-360

1

2

7

6

8

9

3

10

4

5

11

VC

C

AGN

D

D

GN

D

NC

RXD

TXD

FIR_SEL

LE

AD

MDO

MD1

GN DPAD

COM

LP

T

IR

LPC

GPI

O POR

T

POWER

U4

PC87383

15

16

17

18

8

9

12

6

7

11

10

19

20

14

39

63

13

38

64

21

22

23

24

25

26

27

28

29

30

31

32

33

34

52

50

48

46

45

44

43

42

35

36

37

40

41

47

49

51

53

54

55

56

57

58

59

60

61

62

3

2

1

4

5

GPIO0

GPIO1

NC

NC

IRR X1

IR TX

VS

S

PD 3

GPIO6

VD

D

IRR X2_IR SL0/GPIO17

GPIO2

GPIO3

STB#_WRITE#/TEST#

PD 4

SOUT1/GPIO12

VCORF

LFRAME#

NC

GPIO4

LD RQ#/XOR_OUT

GPIO20

SLC T

PE

BUSY _WAIT#

GPIO22/CLKRUN#

GPIO24/ACK#

GPIO21/LPC PD#

GPIO23/PD 7

VS

S

VD

D

LC LK

PD 6

PD 0

PD 1

NC

LAD1

VD

D

VS

S

PD 2

LAD0

LR ESET#

SERIR Q

PD 5

GPIO5

GPIO7

NC

NC

LAD2

LAD3

ERR #

SLIN#_ASTRB#

INIT#

AFD#_DSTRB#/TRIS#

C LKIN

DCD1#/GPIO16

DSR1#/GPIO15

SIN1/GPIO14

R TS1#/GPIO13

C TS1#/GPIO11

NC

NC

DTR1#_BOUT1/BADDR

RI1#/GPIO10

C55

*10P

2

1

R40

*0

T

C64

4.7U_0805

C53

0.1U

R 46

4.7K

C 54

0.1U

C67

0.1U

C70

4.7U_0805

R735

*0

C 59

0.1U

C62

4.7U_0805

R63

*4.7K

R53

4.7K

T

BASE ADDRESS CONFIGURATION

INTERNAL PULL HI

DTRA# PULL-UP : 4E

DTRA# PULL-DOWN: 2E

(DEFAULT)

XBUS RESET CONFIGURATION

Close to PC87383

FOR 35W LOW POWER CPU ( D VERSION )

D_STEP_CPU into High,

When CPU Entry C3,C4.

LPC

Close to PC87383

5 / 2 0 C h a n g e

5 / 2 0 C h a n g e

R P 6 ( 1 0 P 8 R X 4 . 7 K ) C h a n g e 8 . 2 K .

A D D R 7 3 4 ( 1 0 K ) .