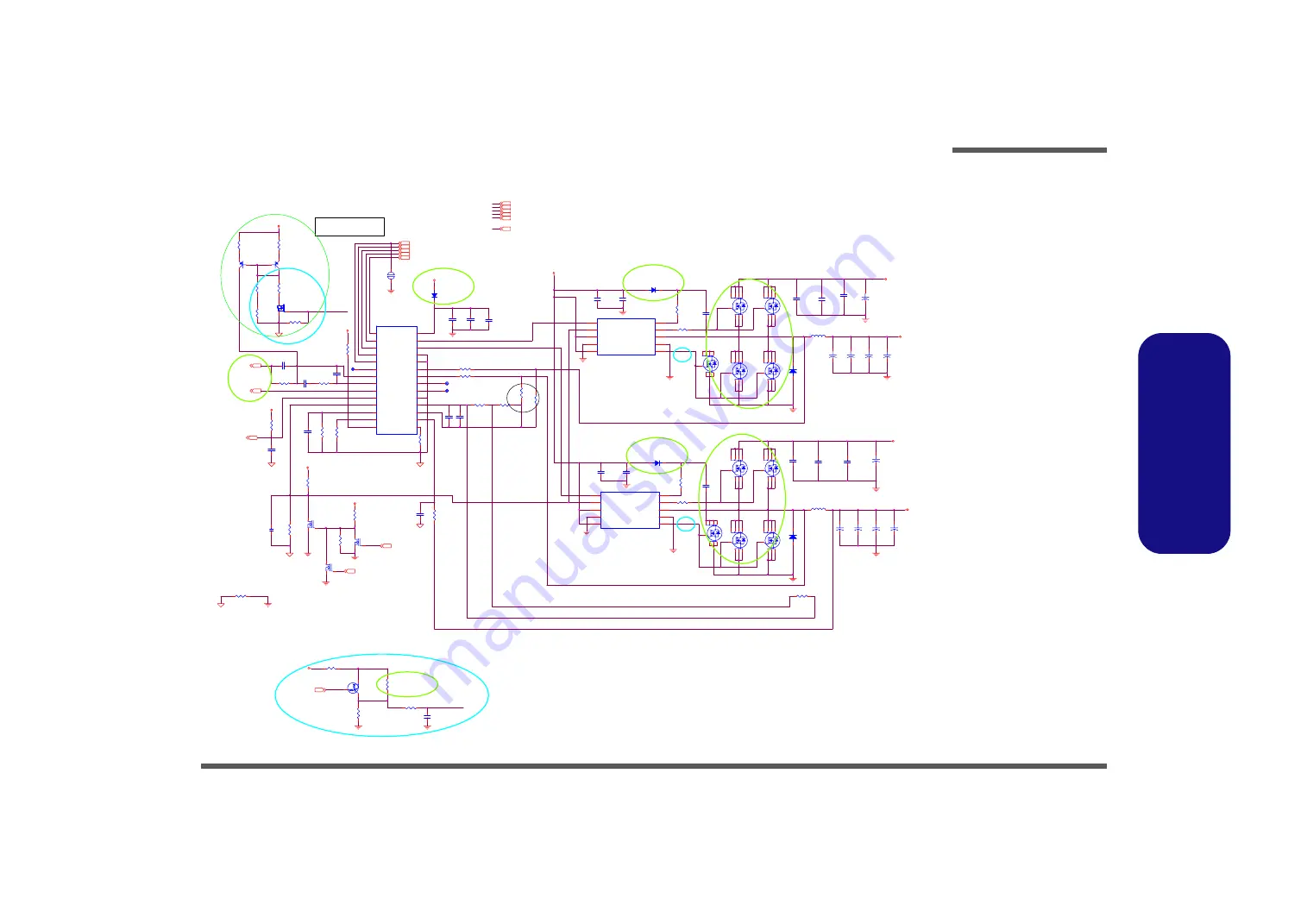

Schematic Diagrams

VCORE B - 33

B.Sch

em

atic D

iag

rams

VCORE

SGND5

+3VS

VCORE

VIN

VIN

VCORE

VIN

+12V

SGND5

SGND5

SGND5

SGND5

+3V

+3V

+VDD5

+3V

SGND5

+3V

VIN 16,29,30,31,34,36

+3V 4,9,10,11,13,14,17,18,19,20,21,22,23,24,26,29,33

+12V 8,20,21,23,26,28,29,30

VCORE 5

+VDD5 9,13,16,19,23,26,29,30,34,36

+3VS 2,4,8,9,10,11,12,13,14,16,18,19,22,23,24,25,28,29,33,35,36

D_STEP_CPU

25

CPU_VID1 4

CPU_VID4 4

CPU_VID2 4

CPU_VID0 4

CPU_VID3 4

VR_PWRGD

9

TEST 29,30

CPUVDD_EN 9

VCORE-

4,5

VCORE+

4,5

Z3232

Z3233

35W CPU

Z3202

35W CPU

Z3231

Z3201

Z3213

Z3216

Z3204

Z3212

Z3217

Z3210

Z3215

Z3218

Z3220

Z3206

Z3211

Z3205

Z3208

Z3209

Z3207

Z3219

Z3214

Z3226

Z3229

Z3221

Z3236

Z3225

Z3222

Z3227

Z3223

Z3230

Z3234

Z3228

Z3224

Z3238

Z3239

Z3240

Z3241

Z3235

Z3203

R853

0

D58

1SS355

A

C

Q21

RQA200N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

+

C562

22U_25

V

_

O

S

1

0

*5

1

2

R736

*0

C135

*1U

R165

100K

Q28

2N7002

G

S

D

R193

124K

C1 2 7

1 0U_1 20 6

+

C578

470U_4V_7343

1

2

+

C573

470U_4V_7343

1

2

C146

0.01U

C148

0 .1 U_ 08 05

C130

0.039U

C143

1U

C124

0.1U

+

C568

470U_4V_7343

1

2

R161

32.4K

U12

ADP3166

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

VID4

VID3

VID2

VID1

VID0

Crowbar

FBRTN

FB

COMP

PWRGD

EN

DELAY

RT

RAMPADJ

ILIMIT

CSREF

CSSUM

CSCOMP

GND

CS4

CS3

CS2

CS1

PWM4

PWM3

PWM2

PWM1

VCC

+

C564

470U_4V_7343

1

2

Q34

MMBT3906

B

E

C

C11 8

1 0U_1 20 6

C81

1U

R191

10

R156

10K

R209

*1M

C1 04

10 U_ 12 06

R155

10K

R174

0

R190

*4.7K

+

C571

470U_4V_7343

1

2

U11

ADP3419

1

2

3

4

5

6

7

8

9

10

IN

SD#

DRVLSD#

CROWBAR

VCC

DRVL

GND

SW

DRVH

BST

Q22

RQA200N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

C147

100P

R188

*0

+

C586

470U_4V_7343

1

2

R194

124K

R168

10K

R208

*100K

D39

SCD34

A

C

J2

JOPEN

1

2

R171

220K

R163

100K

C111

4.7U_0805

R192

43K

+

C566

470U_4V_7343

1

2

Q29

RQA130N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

Q24

RQA130N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

R175

0

Q30

RQA130N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

R189

95.3K

C112

0 .1U_0 80 5

R159

390K

C139

100P

+

C572

470U_4V_7343

1

2

Q41

*DTD114EK

C

E

B

Q25

RQA130N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

C131

680P

R149

8.45K

Q42

*2N7002

G

D

S

C121

4.7U_0805

C119

27P

Q37

RQA200N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

C149

4.7U_0805

RTH1

100K/NTC

C115

680P

+

C563

22U_25V_OS10*5

1

2

L52

0.56uH

Q38

RQA200N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

R158

487K

R157

510K

R164

0_0805

R170

0

C498

0 .1U_0 80 5

Q23

RQA200N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

L53

0.56uH

C145

0.0047U_0805

C152

*0.1U

R160

*40.2K

C109

0.1U

U8

ADP3419

1

2

3

4

5

6

7

8

9

10

IN

SD#

DRVLSD#

CROWBAR

VCC

DRVL

GND

SW

DRVH

BST

R95

0

R152 2K

C151

10U_1206

C5 58

1 0U_ 12 0 6

Q35

MMBT3906

B

E

C

R166

10K

D40

SCD34

A

C

R162

0

Q36

RQA200N03

3

4

8

2

5

6 7

1

..

G

D

S

D,

. D.

,

T426

R111

0

Q33

2N7002

G

S

D

T428

T427

Q32

2N7002

G

S

D

R167

10K

D27

1SS355

A

C

D26

1SS355

A

C

PM_DPRSLPVR into High,

When CPU Entry C3,C4.

FOR 35W LOW POWER CPU ( D VERSION )

D_STEP_CPU into High,

When CPU Entry C3,C4.

20A

20A

1-----LOW POWER TYPE

0-----STANDARD TPYE

35W CPU

Reserve For K8-M

Close to

output

Inductor

5 / 2 0 C h a n g e

D e l S W 3 .

5 / 2 0 C h a n g e

5 / 2 0 C h a n g e

5 / 2 0 C h a n g e

VCORE+ VCORE- Place trace 12 mils.

6 / 1 7 C h a n g e

6 / 2 0 C h a n g e

6 / 2 0 C h a n g e

7/28 Change By

allen

94/11/16 Kevin Change

94/11/16 Kevin Change

94/11/17 Kevin DEL R169

94/11/17 Kevin DEL R96

Sheet 33 of 45

VCORE