Evaluation Kit for CMX979 (engineering samples)

EV9790

2017 CML Microsystems Plc

11

UM9790/1

7

Detailed Description

The EV9790 serves as a demonstrator for the CMX979, a 40-lead VQFN device at location U5.

EV9790 functionality includes:

2700 - 3600 MHz VCO and 16- / 24-bit Fractional-N PLL

IF VCO and Integer-N PLL centred at 900MHz

19.2MHz or optional 38.4MHz VCTCXO, plus external reference input

USB Interface via a PE0003 to a CML standard GUI, to allow script control

7.1

Hardware Description

Full details of the silicon functionality are contained in the CMX979 datasheet. The EV9790 is assembled on a 65 x 69mm,

1.6mm thick 6-layer PCB (reference PCB596B), with the upper layer having a Rogers RO4003C ceramic substrate for low

loss and consistent high frequency performance. The other layers use FR4 / VT481 2116 dielectric.

In general, RF components, connectors and configuration links have been placed on the top layer, with voltage regulators,

supplies and decoupling for the CMX979 on the bottom layer. The layout has been optimised for low ground impedance

and short RF tracking for operation at high frequencies. Gerber files and a BOM can be downloaded from the CML

website.

A high frequency SMA edge connector is used for the J1 output with a Grounded Co-Planar Wave Guide transmission line.

7.1.1

RF VCO /PLL

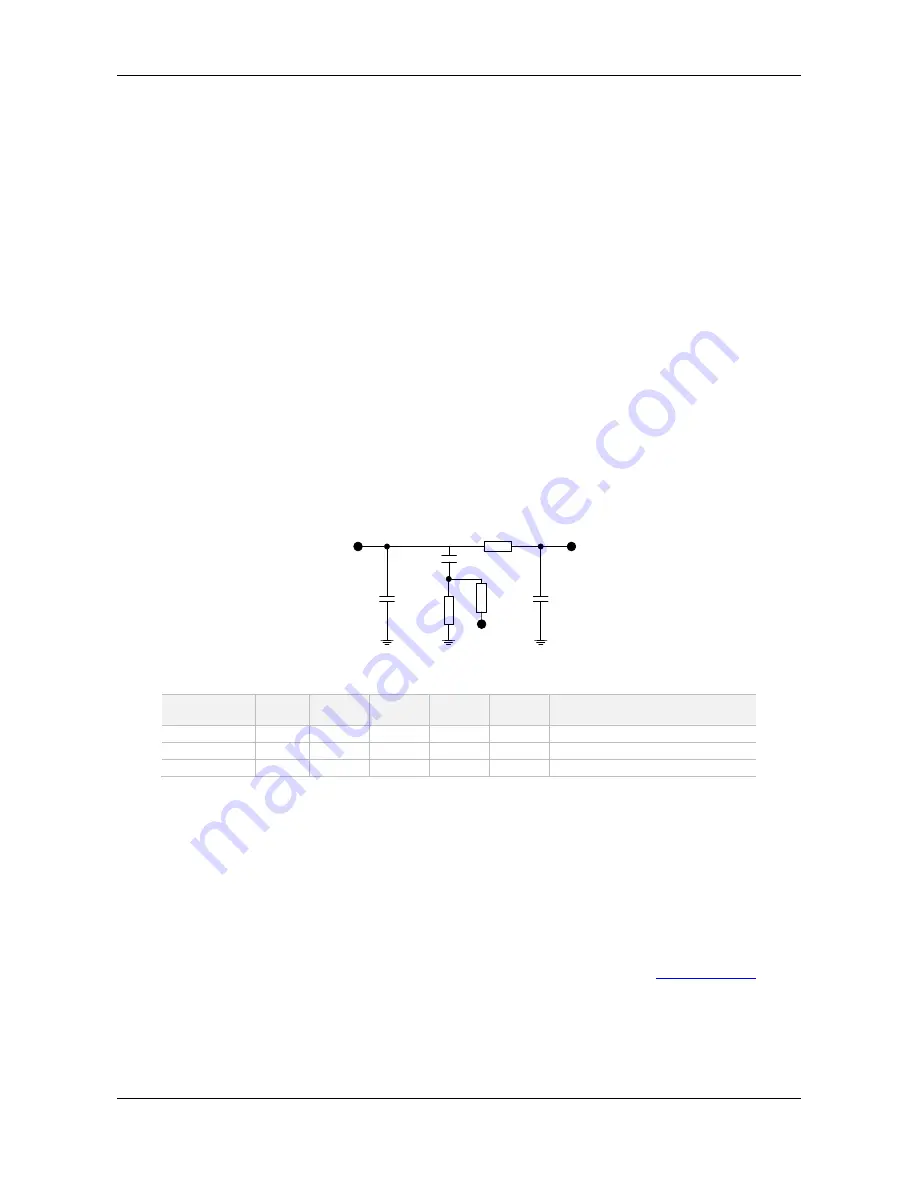

The CMX979 contains a 16- or 24-bit Fractional-N PLL synthesiser used with the on-chip 2700 – 3600 MHz VCO. The loop

filter is external to the IC and can (optionally) incorporate a fast locking function, see Figure 8. The loop filter output is

then routed back to the tuning input of the internal VCO,. The on-chip VCO output is available off-chip either as a

fundamental or divided by 2, 4, 6 or 8 at J1.

C14

C3//

C6

C5

R11

R13

DORF

DOIN

FLCK

(Optional )

R8

(optional)

Figure 8 Example External Components – VCO External Low Pass Filter

VCO

Frequency

C5

C3//C6

C14

R11

R13

R8

(optional FLCK)

2.925GHz

750pF

6.2nF

27pF

1.6k

5.1k

See Datasheet section 7.3.4

3.5GHz

470pF

3.6nF

22pF

2.4k

6.8k

See Datasheet section 7.3.4

Values Fitted

680pF

5.6nF

27pF

2.2k

5.6k

See Datasheet section 7.3.4

Note: C3, C5, C14, R11 and R13 assume a Kvco=70MHz/V, Icp=400uA, Fref=19.2MHz. The values fitted are a compromise

for mid-band operation. These values may require modification for use with other comparison frequencies and charge

pump currents.

Table 7 3

rd

Order Loop Filter Values for a VCO Frequency of 2.925GHz/3.5GHz

7.1.2

IF PLL/VCO

The CMX979 incorporates an additional internal IF VCO and PLL with internal loop filter. The VCO is tuned by external

inductor L3; with the default value fitted the tuning range is centred around 900MHz. The VCO output is available either

as a fundamental or divided by 4, 8 or 16 at the SMA connector J6.

7.1.3

Reference Oscillator

U4 is a GTXO-91T/EI 19.2MHz 0.5 ppm TCXO, part number MP05955, supplied by Golledge (

www.golledge.com

). This is

used as the reference for the RF and IF PLLs within the CMX979 (MCLK). Options are provided to use a lower phase noise

Golledge GTXO-74V/JI 38.4MHz VCTCXO reference, part number MP07489 (footprint U3) or an external reference signal

can be applied to the SMA connector J3. These inputs can also be buffered via U2. The selection of this buffering is via the

link configuration field J2. The VCTCXO tuning inputs can be accessed via test loops TL2 and TL4, to allow the addition of a

modulating signal within the PLL bandwidth. Note that if the alternative oscillator footprint U3 is used, both the supply

resistor R22 and output coupling capacitor C23 should be removed to disable the unused oscillator U4.