Evaluation Kit for CMX979 (engineering samples)

EV9790

2017 CML Microsystems Plc

20

UM9790/1

7.4

Application Information

See Section 5.1 for board setup details and Section 5.2 for operation of the EV9790.

7.4.1

Typical Performance

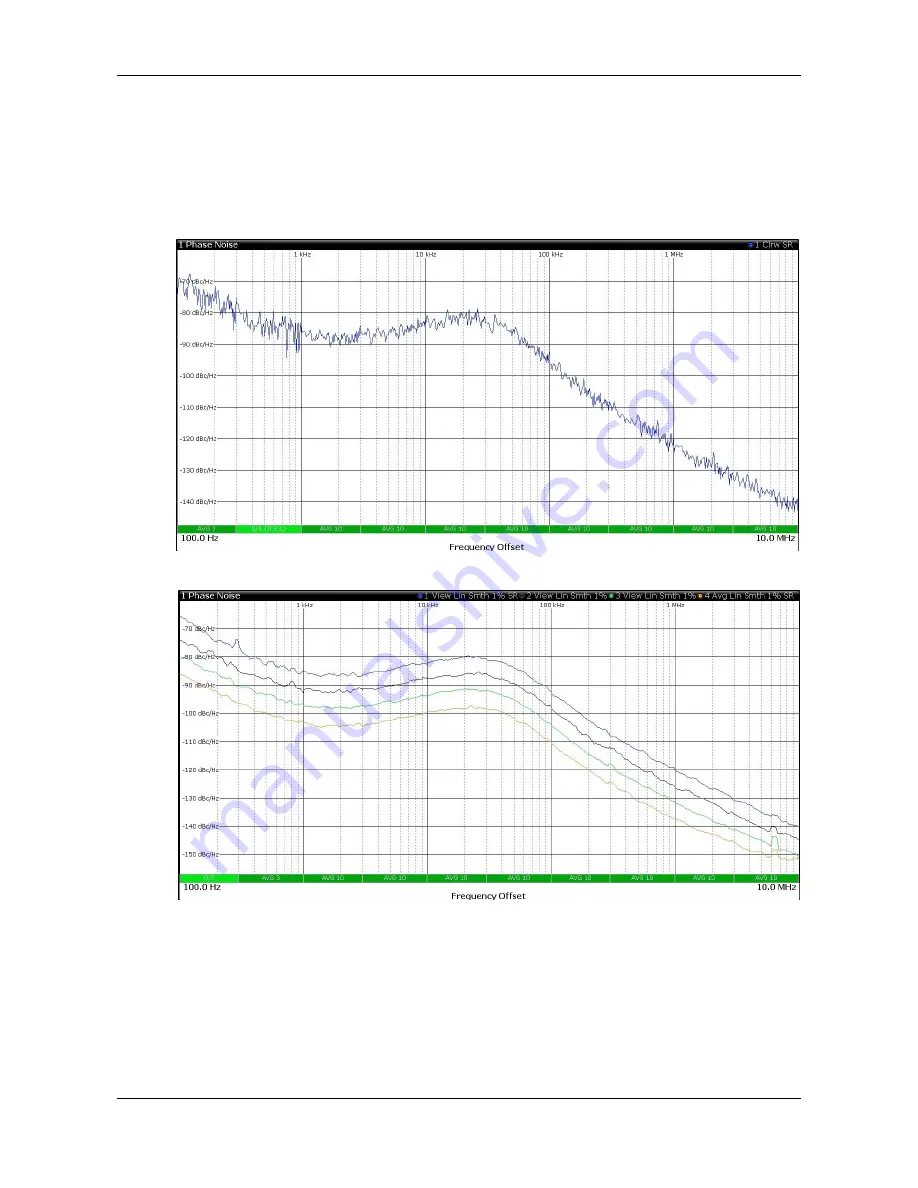

Typical performance for the EV9790 is shown below.

The phase noise profiles can be varied by a number of settings, notably the loop filter bandwidth, comparison frequency,

charge pump current, reference noise, output divider setting, etc.

Figure 18 Phase noise plot of 2.8GHz RF PLL, Icp=400µA, F

Comp

=19.2MHz, PLL type ‘1100’.

Figure 19 Phase noise plot of 3.2GHz RF PLL, Icp=400µA, F

Comp

=19.2MHz, PLL type ‘1100’ also showing output in /2 mode

(1600MHz), /4 mode (800MHz) and /8 mode (400MHz).