Introduction

1-11

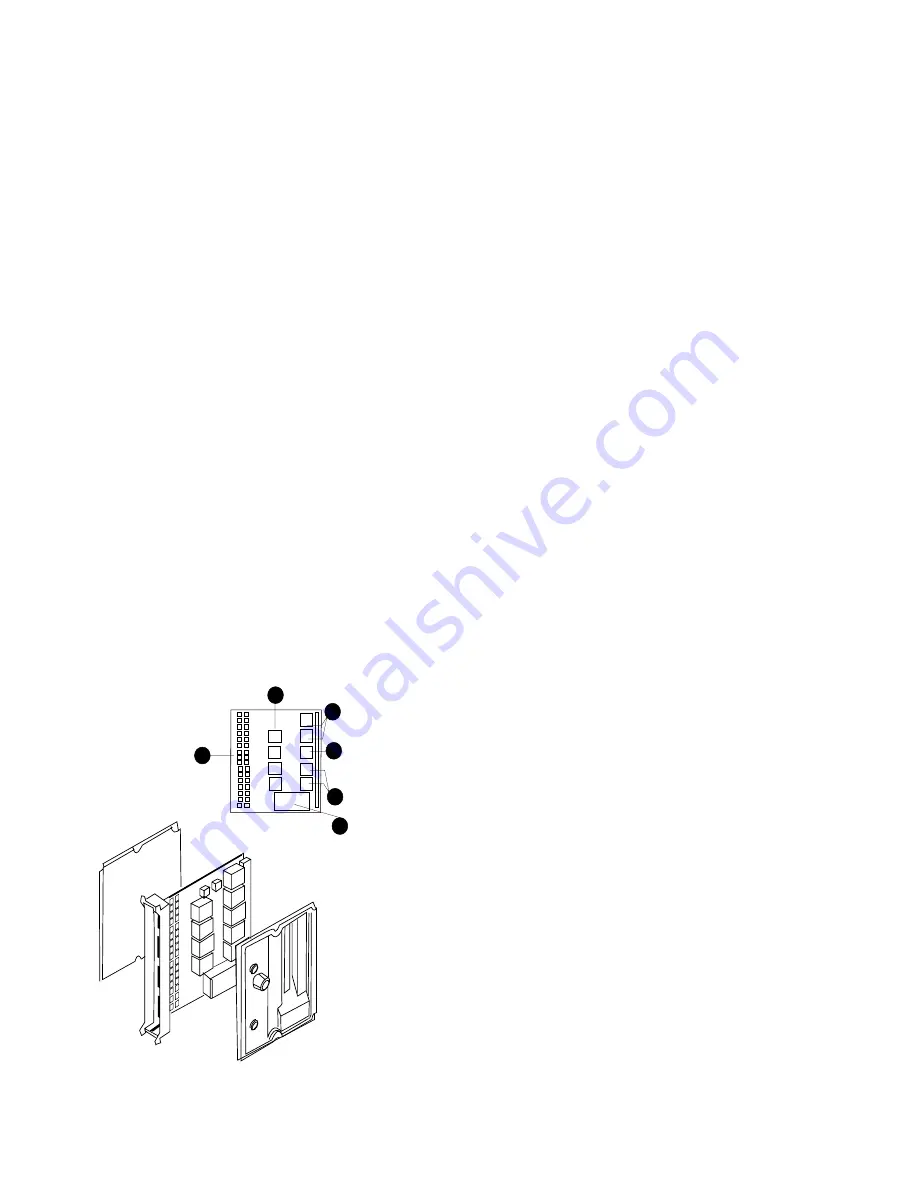

The KFTHA module is designed for high-speed, high-volume data transfers.

Direct memory access (DMA) transfers are pipelined to allow for up to 500

Mbytes/second throughput. The major elements of the KFTHA module are:

➊

RAM to buffer data for the DMA transfers.

➋

Four hose-to-data (HDP) chips, each handling 32 bits from two “hoses”

(I/O cables connecting to an adapter in an associated I/O bus). Data on

the HDPs flow in one direction; either “up” (to the KFTHA) or “down” (to

the I/O adapter).

➌

Four I/O data path (IDP) chips, which together handle a 256-bit data

transfer to or from the TLSB system bus.

➍

An I/O control chip (ICC) houses the primary control logic for the TLSB

interface.

➎

A DC-to-DC converter that converts the 48 VDC system power to the DC

voltage required by the KFTHA module.

Figure 1–6 KFTHA Module

SM16-99

1

3

3

4

2

5