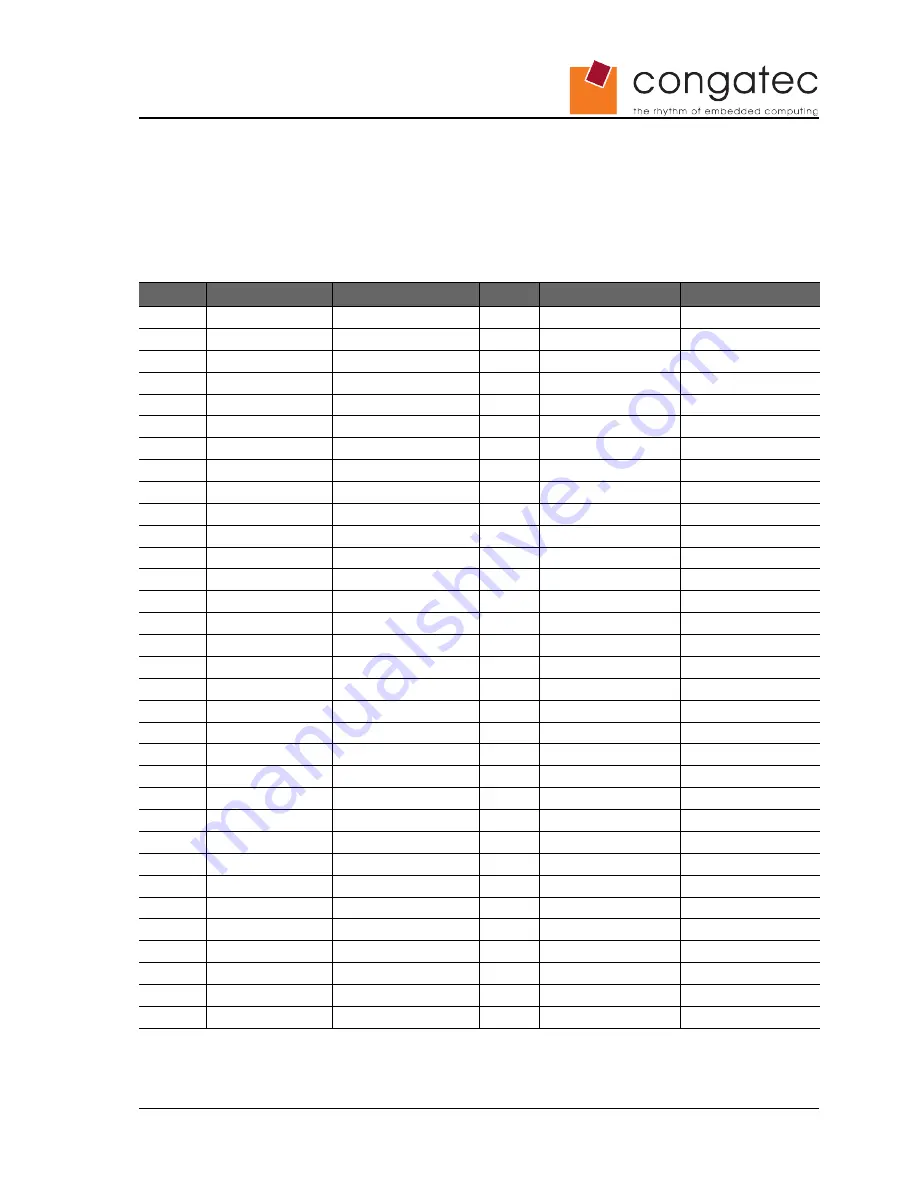

7.4 X2 Connector Pinout

The following table includes a reference column describing the corresponding ETX

standard X2 connector pinout.

Table 15

X2 Connector Pinout

Pin

XTX

TM

Signal

ETX

®

Reference

Pin

XTX

TM

Signal

ETX

®

Reference

1

GND

GND

2

GND

GND

3

PCIE_

SD14

4

S

SD15

5

PCIE_CLK_REF-

SD13

6

SATA0_RX-

MASTER#

7

GND

SD12

8

GND

DREQ7

9

P

SD11

10

SATA0_TX-

DACK7#

11

PCIE3_TX-

SD10

12

S

DREQ6

13

GND

SD9

14

5V_SB

DACK6#

15

P

SD8

16

S

DREQ5

17

PCIE3_RX-

MEMW#

18

SATA1_RX-

DACK5#

19

VCC

MEMR#

20

5V_SB

DREQ0

21

EXC1_CPPE#

LA17

22

SATA1_TX-

DACK0#

23

EXC1_RST#

LA18

24

S

IRQ14

25

USBP5

LA19

26

GND

IRQ15

27

USBP5#

LA20

28

S(*)

IRQ12

29

GND

LA21

30

SATA2_RX-(*)

IRQ11

31

P

LA22

32

SUS_STAT#

IRQ10

33

PCIE2_TX-

LA23

34

PCI_CLKRUN#

IO16#

35

GND

GND

36

GND

GND

37

P

SBHE#

38

SATA2_TX-(*)

M16#

39

PCIE2_RX-

SA0

40

S(*)

OSC

41

EXC0_CPPE#

SA1

42

GND

BALE

43

EXC0_RST#

SA2

44

S(*)

TC

45

USBP4

SA3

46

SATA3_RX-(*)

DACK2#

47

USBP4#

SA4

48

WDTRIG

IRQ3

49

SLP_S3#

SA5

50

SATALED#

IRQ4

51

VCC

VCC

52

VCC

VCC

53

PCIE1_RX-

SA6

54

SATA3_TX-(*)

IRQ5

55

P

SA7

56

S(*)

IRQ6

57

GND

SA8

58

IL_SATA#

IRQ7

59

PCIE1_TX-

SA9

60

PP_TPM

SYSCLK

61

P

SA10

62

RESERVED

REFSH#

63

PCE_WAKE#

SA11

64

PCI_GNT#A(*)

DREQ1

65

SLP_S5#

SA12

66

PCI_REQ#A(*)

DACK1#

Copyright © 2006 congatec AG

X945m13

51/102