Summary of Contents for 32K Bytesaver

Page 1: ...Cromemeo 31K Bytesaver Five Dollars ...

Page 5: ......

Page 7: ......

Page 25: ... ...

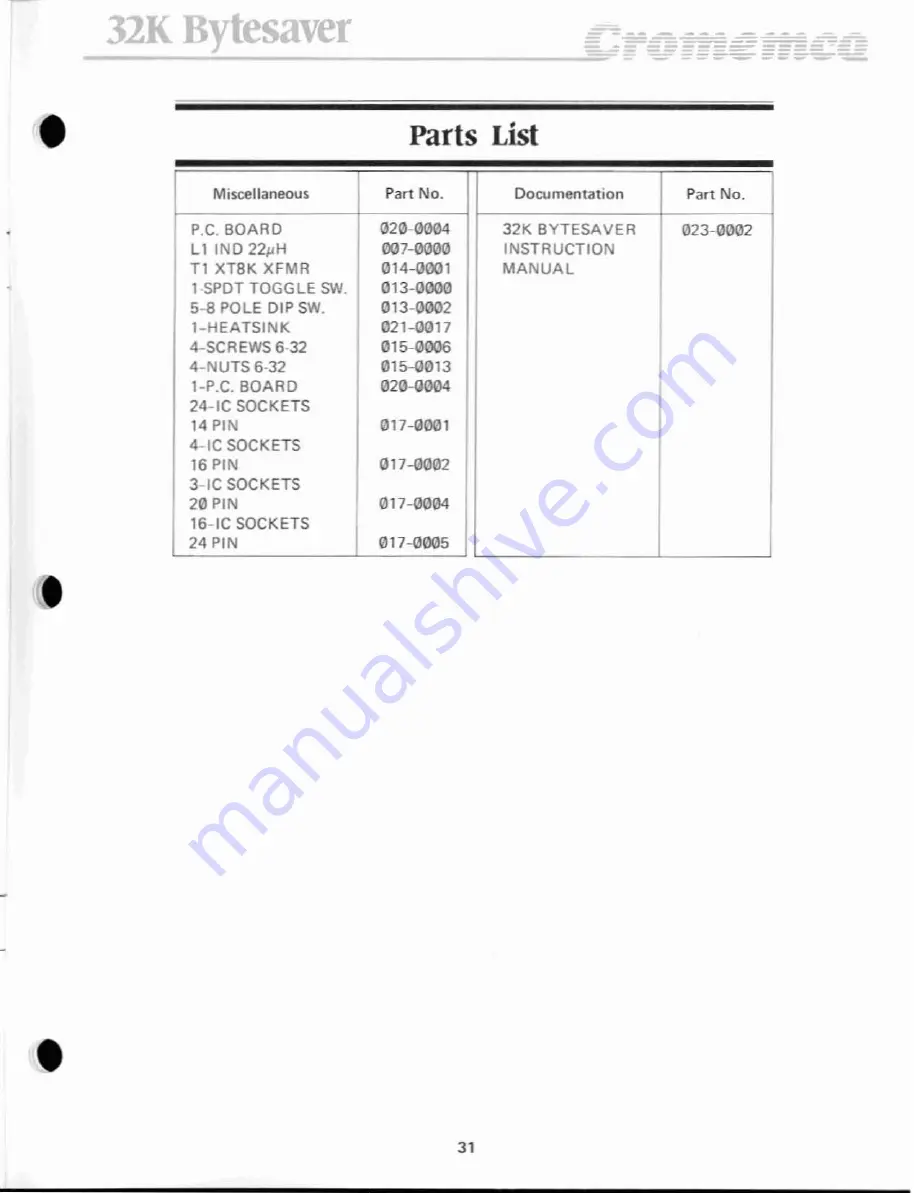

Page 31: ... ...

Page 35: ......

Page 41: ...32K Bytesaver ParlsLocationDiagram 7 IS1 H M Of IN UH CJl 32 ...

Page 44: ... I db I c s 8 s e or e __ _ _ I_ s s t s s e fr J B S o l _ I I L t I l j 7 I 1 t I _ 0 _ ...

Page 45: ... l et4 e Ju 321 8 tu4 C f P CI IOlOEOOl D _ I 1tIill Y r c r _ _ _ _ _ I f _ b a 1 B S B ...

Page 46: ...023 0002 ...