Chapter 7 Clock & Synchronization

55

CPU

Sys

Alarm

Alarm

I /O

Normal

E1

T D

RD

Alarm

Loss

Loss

Sig

S ync

Err

On Line

E1

TD

RD

Alarm

Loss

Loss

Sig

Sync

Err

On Line

N¡Á64K

A larm

R D1

T D2

R D2

T D1

N¡Á64K

Alarm

RD1

T D2

RD2

T D1

64K/

128K

A larm

RD3

RD2

T D1

RD1

T D2

T D3

64K/

128K

Alarm

RD3

RD2

TD1

RD1

TD2

TD3

64K/

128K

Alarm

RD3

RD2

T D1

RD1

T D2

T D3

X.50

Alarm

Loss

Sync

TD1

RD1

TD2

RD2

RD3

TD3

TD4

RD4

TD5

RD5

X.50

Alarm

Loss

Sync

T D1

RD1

T D2

RD2

RD3

T D3

T D4

RD4

T D5

RD5

Sync

N¡Á64K

Alar m

RD1

TD2

RD2

TD1

ASYNC

Alarm

T D2

RD 2

T D1

RD 1

T D3

RD 3

T D4

RD 4

ASYNC

Alarm

T D2

RD2

T D1

RD1

T D3

RD3

T D4

RD4

POWER

ON

POWER

ON

unio n

union

ERM-MUX

ERM-MUX

CPU

Sys

Alarm

Alarm

I/O

Normal

E1

TD

RD

Alarm

Loss

Loss

Sig

Sync

Err

On Line

E1

T D

R D

Alarm

Loss

Loss

Sig

Sync

Err

On Line

N¡Á64K

Alarm

RD1

T D2

RD2

T D1

N¡Á64K

Alar m

RD1

TD2

RD2

TD1

64K/

128K

Alarm

RD3

RD2

TD1

RD1

TD2

TD3

64K/

128K

Alarm

RD 3

RD 2

T D1

RD 1

T D2

T D3

64K/

128K

Alarm

RD3

RD2

T D1

RD1

T D2

T D3

X.50

Alarm

Loss

Sync

T D1

RD1

T D2

RD2

RD3

T D3

T D4

RD4

T D5

RD5

X.50

Alar m

Loss

Sync

TD 1

RD1

TD 2

RD2

RD3

TD 3

TD 4

RD4

TD 5

RD5

S ync

N¡Á64K

Alarm

RD1

TD2

RD2

TD1

ASYNC

Alarm

T D2

RD2

T D1

RD1

T D3

RD3

T D4

RD4

ASYNC

Alarm

TD2

RD2

TD1

RD1

TD3

RD3

TD4

RD4

POWER

ON

P OWER

ON

union

un ion

ERM-MUX

ERM-MUX

DCE

DTE

DTE

DCE

A

B

DDN

Chapter 7 Clock & Synchronization

This chapter details the clocking schemes supported by the ERM-MUX/Plus.

7.1 Setting clock for whole machine

7.1.1 E1A1-8's Recover clock

MUX/PLUS will pick up recovery clock from E1A1 line received signal, and treat it as the clock source for the whole

machine.

7.1.2 Internal clock

This clock source is the crystal clock source in ERM-MUX/PLUS.

7.1.3 I/O card clock

I/O card clock is provided by CH1 data port of specified SLOT-n. The IO cards that support such functions include:

N64K/V35 card, A/SYNC-128K card, SUB-E1 card, and G703-64K cards.

7.1.4 G703 external clock

The external clock source (Network Clock) will be connected to the BNC socket or RJ-45 connector (PIN4/PIN5) on back card

for external clock, and so the G.703 external clock is the system source.

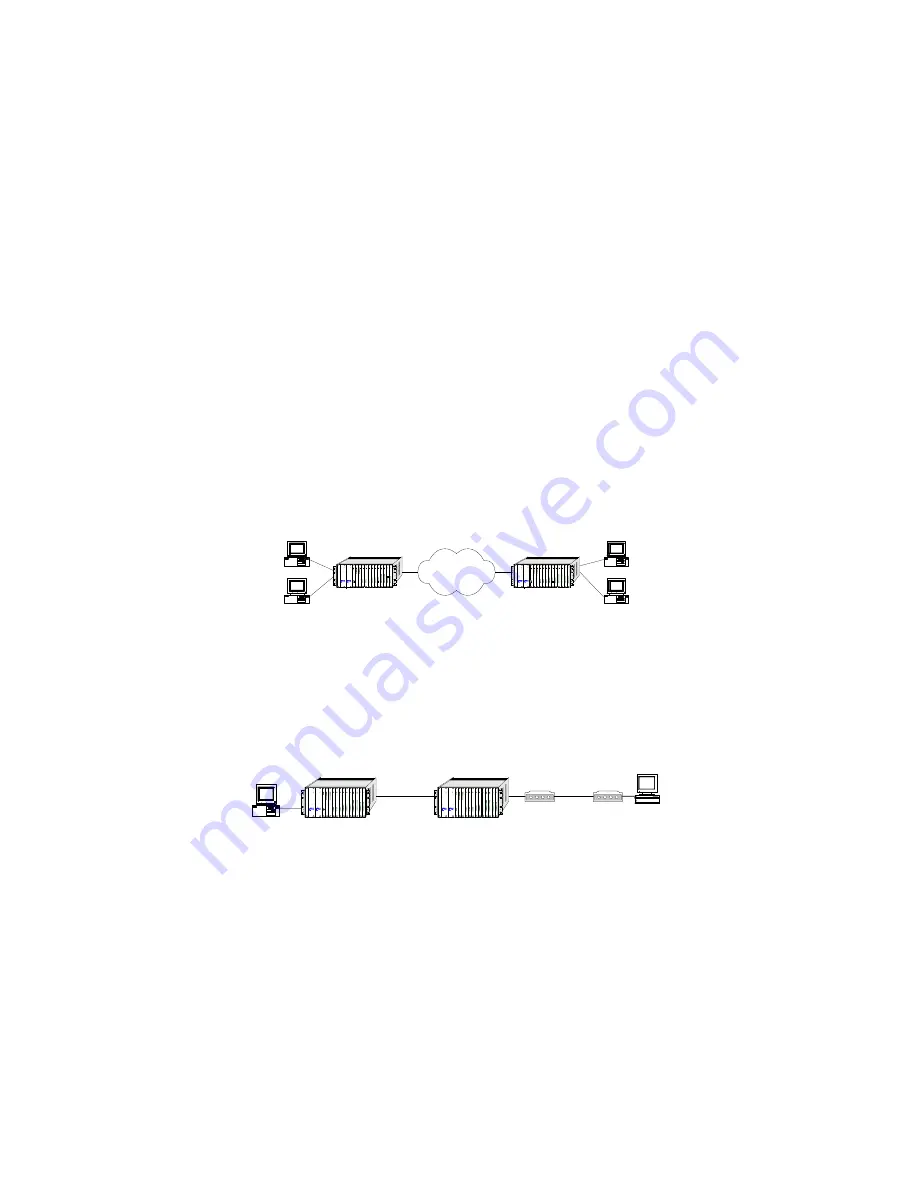

7.2 Connection between multiplexer and synchronous terminal device

In the following examples, the clock setting methods are described.

Figure 7.1 The direct connection between multiplexer and synchronization terminal device

Both of MUX/PLUS A and B can adopt recovery clock, or one recovery clock and other internal clock. All terminal devices

can use RC and TC timing. Terminal device and MUX/PLUS are connected via straight cable.

7.3 MUX with synchronization tail circuit

Figure 7.2 MUX/PLUS with synchronization tail circuit

The E1 clock of MUX/PLUS A is set with internal clock and MUX/PLUS B adopts recovery clock. The clock for MODEM A

is set as external clock (receiving timing from data port) and the clock for MODEM B is set as the loop clock.

MODEM A and MUX/PLUS B are connected via cross-over cable (DCE to DCE), and all other interface cable for terminals

are straight (DCE to DTE).

CP U

Sys

Alarm

Alarm

I /O

Normal

E1

TD

RD

Al ar m

Los s

Los s

Sig

S ync

Er r

On Line

E1

TD

RD

Alarm

Los s

Los s

Si g

Sync

Err

On Line

N¡Á64K

A larm

RD 1

TD 2

RD 2

TD 1

N¡Á64K

Al ar m

RD1

TD2

RD2

TD1

64K/

128K

Al arm

R D3

R D2

T D1

R D1

T D2

T D3

64K/

128K

Al ar m

R D3

R D2

T D1

R D1

T D2

T D3

64K/

128K

Al ar m

R D3

R D2

T D1

R D1

T D2

T D3

X.50

Al ar m

Los s

S ync

TD 1

RD 1

TD 2

RD 2

RD 3

TD 3

TD 4

RD 4

TD 5

RD 5

X.50

Al ar m

Los s

S ync

T D1

R D1

T D2

R D2

R D3

T D3

T D4

R D4

T D5

R D5

S ync

N¡Á64K

Al ar m

RD1

TD2

RD2

TD1

ASYNC

Al ar m

TD 2

RD 2

TD 1

RD 1

TD 3

RD 3

TD 4

RD 4

ASYNC

Alarm

TD2

RD2

TD1

RD1

TD3

RD3

TD4

RD4

P OW ER

ON

P OW ER

ON

union

union

ERM-MUX

ERM-MUX

MODEM

MODEM

终端

模拟线路

B

A

CPU

S ys

Alar m

Alar m

I/O

Normal

E1

TD

RD

Al ar m

Los s

Los s

Sig

S ync

Er r

On Line

E1

TD

RD

Al ar m

Los s

Los s

Si g

Sync

Er r

On Line

N¡Á64K

A larm

RD 1

TD 2

RD 2

TD 1

N¡Á64K

A larm

RD 1

TD 2

RD 2

TD 1

64K/

128K

A larm

R D3

R D2

T D1

R D1

T D2

T D3

64K/

128K

A larm

RD3

RD2

TD1

RD1

TD2

TD3

64K/

128K

Al ar m

R D3

R D2

T D1

R D1

T D2

T D3

X.50

A larm

Los s

Sync

T D1

R D1

T D2

R D2

R D3

T D3

T D4

R D4

T D5

R D5

X.50

Al arm

Loss

Sync

T D1

R D1

T D2

R D2

R D3

T D3

T D4

R D4

T D5

R D5

S ync

N¡Á64K

Al arm

RD 1

TD 2

RD 2

TD 1

ASYNC

Al ar m

TD 2

RD 2

TD 1

RD 1

TD 3

RD 3

TD 4

RD 4

ASYNC

Al ar m

TD 2

RD 2

TD 1

RD 1

TD 3

RD 3

TD 4

RD 4

P OW ER

ON

P OW ER

ON

union

union

ERM-MUX

ERM-MUX

E1

线路

甲

乙

终端

Local -A

Remote -B

DTE

DTE

E1

Leased line

Summary of Contents for ERM-MUX

Page 1: ...ERM MUX Plus E1 Multi Service Access Multiplexer ...

Page 2: ......

Page 8: ...Table of Contents ...

Page 20: ...Chapter 2 Installation 20 This page was left blank intentionally ...

Page 30: ...Chapter 3 LED Indicators and Cable Pin Definitions 30 This page was left blank intentionally ...

Page 58: ...Chapter 8 Application Notes 58 This page was left blank intentionally ...

Page 59: ......

Page 60: ......