Pin Information

32

CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

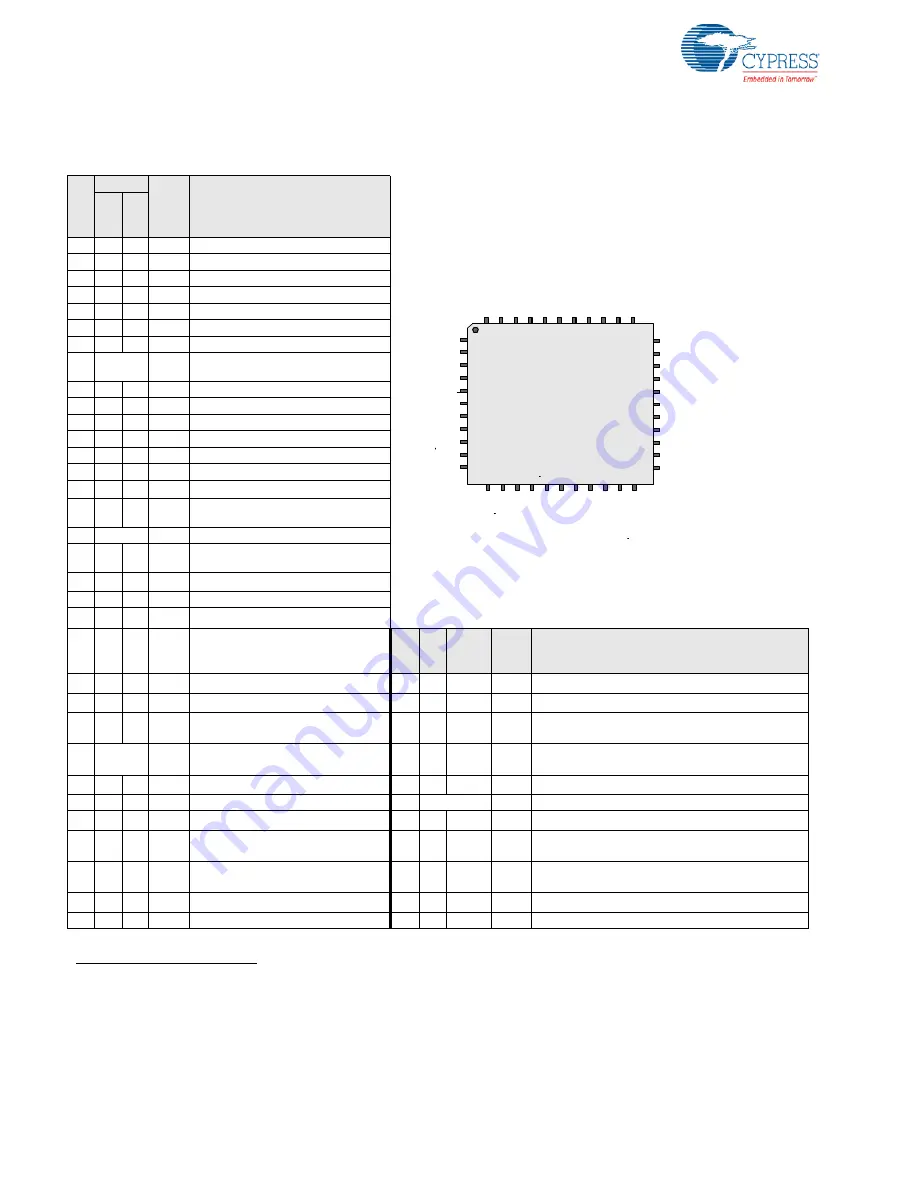

1.1.3

44-Pin Part Pinouts

Table 1-3. 44-Pin Part Pinout (TQFP)

Pin

No.

Type

Pin

Name

Description

CY8C28513, CY8C28533, and CY8C28545 PSoC Devices

Di

g

it

a

l

An

a

lo

g

1

I/O

M

P2[5]

2

I/O

I, M P2[3]

Direct switched capacitor block input.

3

I/O

I, M P2[1]

Direct switched capacitor block input.

4

I/O

M

P4[7]

5

I/O

M

P4[5]

6

I/O

M

P4[3]

7

I/O

M

P4[1]

8

Output

SMP

Switch Mode Pump (SMP) connection to

external components.

9

I/O

M

P3[7]

10

I/O

M

P3[5]

11

I/O

M

P3[3]

12

I/O

M

P3[1]

13

I/O

M

P1[7]

I2C0 Serial Clock (SCL)

14

I/O

M

P1[5]

I2C0 Serial Data (SDA)

15

I/O

M

P1[3]

16

I/O

M

P1[1]*

Crystal (XTALin), I2C0 Serial Clock

(SCL), ISSP-SCLK

17

Power

Vss

Ground connection

18

I/O

M

P1[0]*

Crystal (XTALout), I2C0 Serial Data

(SDA), ISSP-SDATA

19

I/O

M

P1[2]

I2C1 Serial Data (SDA)

a

a. CY8C28x52, CY8C28x13, and CY8C28x33 devices only have one I

2

C block. Therefore, this GPIO does not function as an I

2

C pin for these devices.

20

I/O

M

P1[4]

Optional External Clock Input (EXTCLK)

21

I/O

M

P1[6]

I2C1 Serial Clock (SCL)

a

22

I/O

M

P3[0]

I2C1 Serial Data (SDA)

a

Pin

No.

Digit

a

l

Analog

Name

Description

23

I/O

M

P3[2]

I2C1 Serial Clock (SCL)

a

34

I/O

M

P2[6]

External Voltage Reference (VRef) input.

24

I/O

M

P3[4]

35

I/O

I, M, S

P0[0]

Analog column mux and SAR ADC input

b

b. CY8C28x52 and CY8C28x23 devices do not have a SAR ADC. Therefore, this pin does not function as a SAR ADC input for these devices.

25

I/O

M

P3[6]

36

I/O

I/O, M

S

P0[2]

Analog column mux and SAR ADC input. Analog column

output

b, c

c. CY8C28x33, CY8C28x23, CY8C28x13, and CY8C28x03 devices do not have an analog output buffer for this pin. Therefore, this pin does not function as

an analog column output for these devices.

26

Input

XRES

Active high pin reset with internal pull

down.

37

I/O

I/O, M,

S

P0[4]

Analog column mux and SAR ADC input. Analog column

output

b, c

27

I/O

M

P4[0]

38

I/O

I, M, S

P0[6]

Analog column mux and SAR ADC input

b

28

I/O

M

P4[2]

39

Power

Vdd

Supply voltage.

29

I/O

M

P4[4]

40

I/O

I, M, S

P0[7]

Analog column mux and SAR ADC input

b

30

I/O

M

P4[6]

41

I/O

I/O, M,

S

P0[5]

Analog column mux and SAR ADC input. Analog column

output

b, d

d. CY8C28x13 and CY8C28x03 devices do not have any analog output buffers. Therefore, this pin does not function as an analog column output for these

devices.

31

I/O

I, M P2[0]

Direct switched capacitor block input

e

e. This pin is not a direct switched capacitor block analog input for CY8C28x03, CY8C28x13, CY8C28x23, and CY8C28x33 devices.

42

I/O

I/O, M,

S

P0[3]

Analog column mux and SAR ADC input. Analog column

output

b, d

32

I/O

I, M P2[2]

Direct switched capacitor block input

e

43

I/O

I, M, S

P0[1]

Analog column mux and SAR ADC input

b

33

I/O

M

P2[4]

External Analog Ground (AGND) input.

44

I/O

P2[7]

LEGEND

A = Analog, I = Input, O = Output, S = SAR ADC Input, and M = Analog Mux Bus Input.

* These are the ISSP pins, which are not High Z at POR (Power On Reset).

TQ FP

44

43

42

41

40

39

38

37

36

35

34

13

14

15

16

17

18

19

20

21

22

12

1

2

3

4

5

6

7

8

9

10

11

M , P2[5]

AI, M , P2[3]

AI, M , P2[1]

M , P4[7]

M , P4[5]

M , P4[3]

M , P4[1]

SM P

M , P3[7]

M , P3[5]

M , P3[3]

M, P3[1

]

I2

C

0

S

C

L

,

M,

P1[7

]

I2

C

0

S

D

A

,

M,

P1[5

]

M, P1[3

]

I2

C

0

S

C

L,

XTA

L

in

, M,

P1[1

]

Vs

s

I2

C

0

SD

A,

X

T

AL

out

, M,

P1[0

]

I2

C

1

S

D

A

,

M,

P1[2

]

EX

T

C

L

K

, M

,

P

1

[4

]

I2

C

1

S

C

L

,

M,

P1[6

]

I2

C

1

S

D

A

,

M,

P3[0

]

P2[4], M , External AG N D

P2[2], M , AI

P2[0], M , AI

P4[6], M

P4[4], M

P4[2], M

P4[0], M

XR ES

P3[6], M

P3[4], M

P3[2], M , I2C 1 SC L

P2

[7

],

M

P0

[1

],

M

,

A

I,

S

P0

[3

],

M

,

A

IO, S

P0

[5

],

M

,

A

IO, S

P0

[7

],

M

,

A

I,

S

Vd

d

P0

[6

],

M

,

A

I,

S

P0

[4

],

M

,

A

IO, S

P0

[2

],

M

,

A

IO, S

P0

[0

],

M

,

A

I,

S

P2

[6

],

M

,

E

x

ter

nal VRe

f

33

32

31

30

29

28

27

26

25

24

23

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...