50

CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

Supervisory ROM (SROM)

The following code example puts the correct value in KEY1

and KEY2. The code is preceded by a HALT, to force the

program to jump directly into the setup code and not acci-

dentally run into it.

1.

halt

2. SSCOP: mov [KEY1], 3ah

3.

mov X, SP

4.

mov A, X

5.

add A, 3

6.

mov [KEY2], A

3.1.1

Additional SROM Feature

The SROM has these feature.

Return Codes:

Return codes aid in the determination of

success or failure of a particular function. The return code is

stored in KEY1’s position in the parameter block. The

CheckSum and TableRead functions do not have return

codes because KEY1’s position in the parameter block is

used to return other data.

Note

Read, write, and erase operations may fail if the target

block is read or write protected. Block protection levels are

set during device programming and cannot be modified from

code in the PSoC device.

3.1.2

SROM Function Descriptions

3.1.2.1

SWBootReset Function

The SROM function SWBootReset is responsible for transi-

tioning the device from a reset state to running

code.

See

for more information on

what events causes the SWBootReset function to execute.

The SWBootReset function is executed whenever the

SROM is entered with an M8C accumulator value of 00h;

the SRAM parameter block is not used as an input to the

function. This happens, by design, after a

because the M8C's accumulator is reset to 00h or when

user code executes the SSC instruction with an accumulator

value of 00h.

If the

of the calibration data is valid, the

SWBootReset function ends by setting the internal M8C reg-

isters to 00h, writing 00h to most SRAM addresses in SRAM

Page 0, and then begins to execute user code at address

0000h. (See

and the following paragraphs for

more information on which SRAM addresses are modified.)

If the checksum is not valid, an internal reset is executed

and the boot process starts over. If this condition occurs, the

internal reset status bit (IRESS) is set in the CPU_SCR1

register.

In PSoC devices with more than 256 bytes of SRAM, no

SRAM is modified by the SWBootReset function in SRAM

pages numbered higher than ‘0’.

documents the value of all the SRAM addresses in

Page 0 after a successful SWBootReset. A value of “xx”

indicates that the SRAM address is not modified by the

SWBootReset function. A hex value indicates that the

address should always have the indicated value after a suc-

cessful SWBootReset. A “??” indicates that the value, after

a SWBootReset, is determined by the value of the IRAMDIS

bit in the CPU_SCR1 register. If IRAMDIS is not set, these

addresses will be initialized to 00h. If IRAMDIS is set, these

addresses will not be modified by a SWBootReset after a

watchdog reset.

The IRAMDIS bit allows the preservation of variables even if

a watchdog reset (WDR) occurs. The IRAMDIS bit is reset

by all system resets except watchdog reset. Therefore, this

bit is only useful for watchdog resets and not general resets.

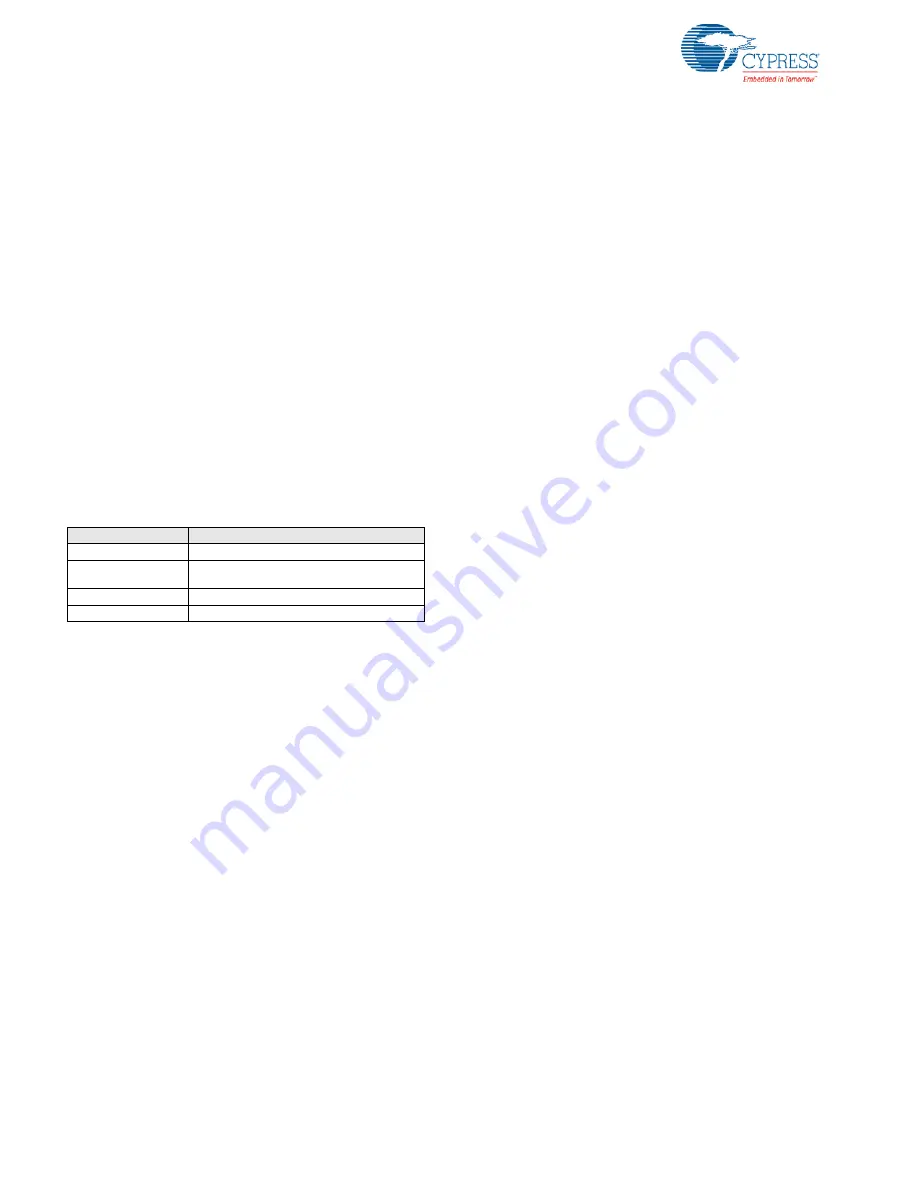

Table 3-3. SROM Return Code Meanings

Return Code Value

Description

00h

Success

01h

Function not allowed due to level of protection on

the block.

02h

Software reset without hardware reset.

03h

Fatal error, SROM halted.

Summary of Contents for CY8C28 series

Page 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Page 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Page 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Page 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Page 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...