FX3 Programmers Manual, Doc. # 001-64707 Rev. *C

45

FX3 Overview

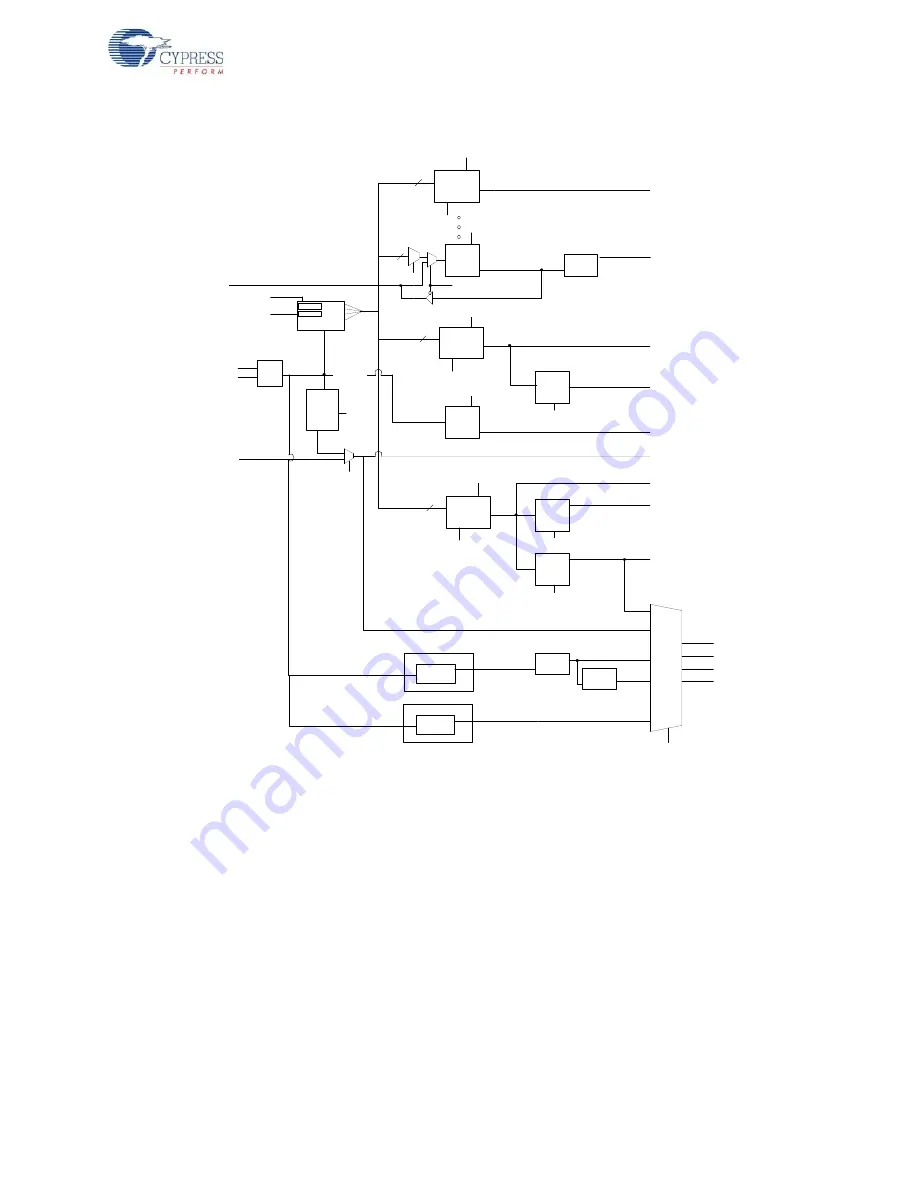

Figure 3-18. Clock Generation Structure

The CPU, DMA, and MMIO clock domains are synchronous to each other. However, every

peripheral assumes its core clock to be fully asynchronous from other peripheral core clocks, the

computing clock or the wakeup clock.

If the core (peripheral) clock is faster than the bus clock, the DMA adapter for the block runs in the

core clock domain. The DMA adapter takes care of the clock crossing on it's interconnect side. If the

core clock is slower than the bus clock, the DMA adapter for that block runs in the bus clock domain.

The DMA adapter takes care of the clock crossing on its core IP side.

CLKIN

MULTIPLY

DIVIDE

CLKOUT_1

CLKOUT_2

CLKOUT_4

CLKOUT_16

SYS_PLL

PLL_SYS_

CLKS[3:0]

PLL_SYS_

CLK_SEL

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

CSD

PLL_SYS_

CLKS[3:0]

PLL_SYS_

CLK_SEL

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

CSD

CLKIN

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

%

PLL_SYS_

CLKS[3:0]

PLL_SYS_

CLK_SEL

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

CSD

CLKIN

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

%

CLKIN

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

%

CLKIN

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

%

CLKIN

SEL_CLK

_DIV[N:0]

DIV_CLK

_OUT

%

Xtal

Osc

CL

K

IN

SE

L

_C

LK

_D

IV

[N

:0]

DI

V

_CL

K

_O

U

T

%

USB2PHY

PLL

CLKIN

CLKOUT_480

CLKOUT_30

USB3PHY

PLL

CLKIN

CLKOUT_125

CLKOUT_5G

CLKIN

DIV_CLK

_OUT

% 4

CLKIN

DIV_CLK

_OUT

% 4

UIB CLK

MUX

uib_epm_clk

uib_hd3_clk

uib_sie_clk

uib_p_clk

reference clock

peripheral_core_clk

i2s_core_clk

gpio_fast_clk

gpio_core_clk

gpio_slow_clk

gpio_standby_clk

cpu_core_clk

mmio_bus_clk

dma_bus_clk

dma_bus_clk_i

standby_clk_i

usb2_clk120_i

usb2_clk30_i

usb3_clk125_i

Clk_32_in

Crystal_in

Crystal_out

PLL_CFG.DIV

PLL_CFG.MUL

mclk_i2s_in

FX3_PERIPH_CLK_CFG.

SYSCLK_SEL

FX3_I2S_CLK_CFG.

SELCLK_DIV

FX3_I2S_CLK_CFG.

SYSCLK_SEL

FX3_I2S_CLK_CFG.

SEL_M_CLK

FX3_GPIO_FCLK_CFG.

SYSCLK_SEL

FX3_GPIO_FCLK_CFG.

SELCLK_DIV

PLL_SYS_CLK_SEL

FX3_GPIO_SCLK_CFG.

SELCLK_DIV

FX3_GPIO_CLK_CFG.

SELCLK_DIV

F

X

3

_S

T

A

NDB

Y

_CL

K

_CF

G

.

SEL

C

LK_

D

IV

FX3_CPU_CLK_CFG.

SELCLK_DIV

FX3_CPU_CLK_CFG.

SYSCLK_SEL

FX3_MMIO_CLK_CFG.

SELCLK_DIV

FX3_DMA_CLK_CFG.

SELCLK_DIV

STANDBY_

CLK_SEL

UIB CLOCK

SRCS.CFG

Note…………………………………………………….

UART baud rate is 1/8

th

of uart_core_clk…………..

I2C operating frequency is 1/10

th

of I2C core clock

SPI operating frequency is ½ of spi core clock…….

CLKIN

DIV_CLK

_OUT

% 4

Summary of Contents for EX-USB FX3

Page 8: ...8 FX3 Programmers Manual Doc 001 64707 Rev C Contents...

Page 12: ...12 FX3 Programmers Manual Doc 001 64707 Rev C Introduction...

Page 48: ...48 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Overview...

Page 74: ...74 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Firmware...

Page 76: ...76 FX3 Programmers Manual Doc 001 64707 Rev C FX3 APIs...

Page 84: ...84 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Application Examples...

Page 98: ...98 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Application Structure...

Page 148: ...148 FX3 Programmers Manual Doc 001 64707 Rev C FX3 P Port Register Access...

Page 165: ...FX3 Programmers Manual Doc 001 64707 Rev C 165 FX3 Development Tools Click next...

Page 178: ...178 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Development Tools Click on Apply...

Page 180: ...180 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Development Tools d Start the GDB server...

Page 185: ...FX3 Programmers Manual Doc 001 64707 Rev C 185 FX3 Development Tools...

Page 186: ...186 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Development Tools...

Page 187: ...FX3 Programmers Manual Doc 001 64707 Rev C 187 FX3 Development Tools...

Page 188: ...188 FX3 Programmers Manual Doc 001 64707 Rev C FX3 Development Tools...

Page 192: ...192 FX3 Programmers Manual Doc 001 64707 Rev C GPIF II Designer...