CY7C67200

Document #: 38-08014 Rev. *G

Page 45 of 78

Transmit Ready

(Bit 4)

The Transmit Ready bit is a read only bit that indicates if the

HSS Transmit FIFO is ready for the CPU to load new data for

transmission.

1:

HSS transmit FIFO ready for loading

0:

HSS transmit FIFO not ready for loading

Packet Mode Select

(Bit 3)

The Packet Mode Select bit selects between Receive Packet

Ready and Receive Ready as the interrupt source for the

RxIntr interrupt.

1:

Selects Receive Packet Ready as the source

0:

Selects Receive Ready as the source

Receive Overflow Flag

(Bit 2)

The Receive Overflow Flag bit indicates if the Receive FIFO

overflowed when set. This flag can be cleared by writing a ‘1’

to this bit.

1:

Overflow occurred

0:

Overflow did not occur

Receive Packet Ready Flag

(Bit 1)

The Receive Packet Ready Flag bit is a read only bit that

indicates if the HSS receive FIFO is full with eight bytes.

1:

HSS receive FIFO is full

0:

HSS receive FIFO is not full

Receive Ready Flag

(Bit 0)

The Receive Ready Flag is a read only bit that indicates if the

HSS receive FIFO is empty.

1:

HSS receive FIFO is not empty (one or more bytes is

reading for reading)

0:

HSS receive FIFO is empty

HSS Baud Rate Register [0xC072] [R/W]

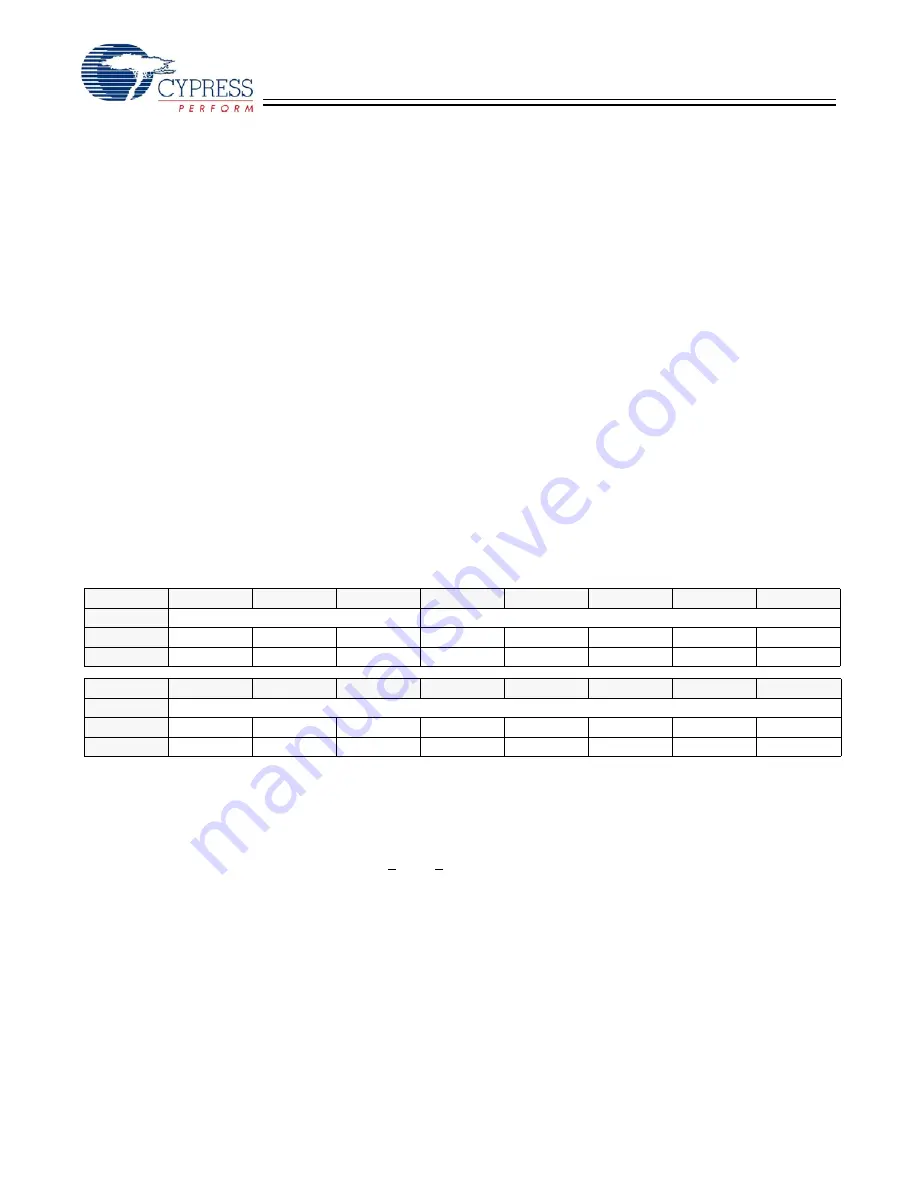

Figure 49. HSS Baud Rate Register

Register Description

The HSS Baud Rate register sets the HSS Baud Rate. At reset, the default value is 0x0017 which sets the baud rate to 2.0 MHz.

Baud

(Bits [12:0])

The Baud field is the baud rate divisor minus one, in units of 1/48 MHz. Therefore the Baud Rate = 48 MHz/(Baud + 1). This puts

a constraint on the Baud Value as follows: (24 – 1) < Baud > (5000 – 1)

Reserved

All reserved bits must bit written as ‘0’.

Bit #

15

14

13

12

11

10

9

8

Field

Reserved

Baud...

Read/Write

-

-

-

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

...Baud

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

1

0

1

1

1

[+] Feedback