CY7C67200

Document #: 38-08014 Rev. *G

Page 51 of 78

SIEXmsg Register [W]

• SIE1msg Register 0x0144

• SIE2msg Register 0x0148

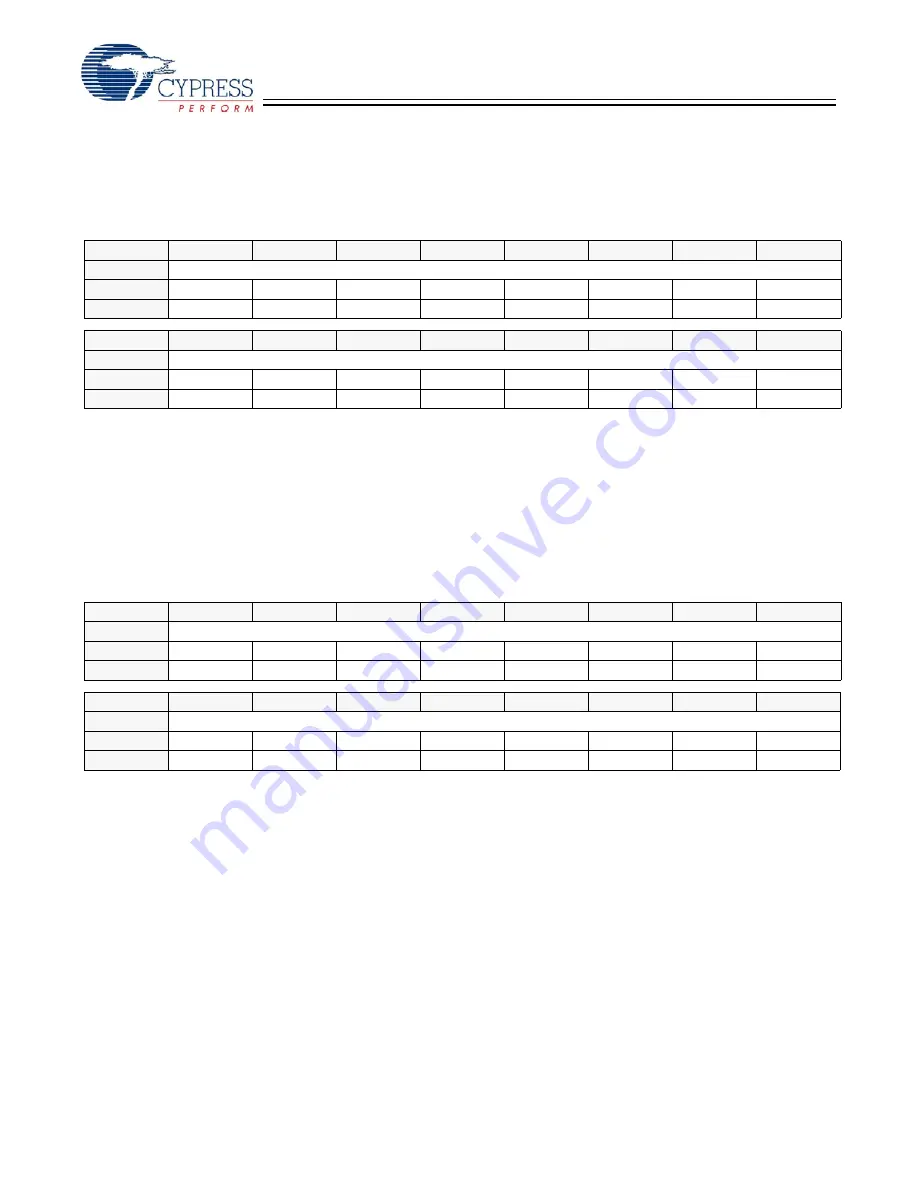

Figure 58. SIEXmsg Register

Register Description

The SIEXmsg register allows an interrupt to be generated on the HPI port. Any write to this register causes the SIEXmsg flag in

the HPI Status Port to go high and also causes an interrupt on the HPI_INTR pin. The SIEXmsg flag is automatically cleared

when the HPI port reads from this register.

Data (Bits

[15:0])

The Data field[15:0] simply must have any value written to it to cause SIExmsg flag in the HPI Status Port to go high.

HPI Mailbox Register [0xC0C6] [R/W]

Figure 59. HPI Mailbox Register

Register Description

The HPI Mailbox register provides a common mailbox between the CY7C67200 and the external host processor.

If enabled, the HPI Mailbox RX Full interrupt triggers when the external host processor writes to this register. When the

CY7C67200 reads this register the HPI Mailbox RX Full interrupt automatically gets cleared.

If enabled, the HPI Mailbox TX Empty interrupt triggers when the external host processor reads from this register. The HPI Mailbox

TX Empty interrupt is automatically cleared when the CY7C67200 writes to this register.

In addition, when the CY7C67200 writes to this register, the HPI_INTR signal on the HPI port asserts signaling the external

processor that there is data in the mailbox to read. The HPI_INTR signal deasserts when the external host processor reads from

this register.

Message

(Bits [15:0])

The Message field contains the message that the host processor wrote to the HPI Mailbox register.

Bit #

15

14

13

12

11

10

9

8

Field

Data...

Read/Write

W

W

W

W

W

W

W

W

Default

X

X

X

X

X

X

X

X

Bit #

7

6

5

4

3

2

1

0

Field

...Data

Read/Write

W

W

W

W

W

W

W

W

Default

X

X

X

X

X

X

X

X

Bit #

15

14

13

12

11

10

9

8

Field

Message...

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit #

7

6

5

4

3

2

1

0

Field

...Message

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

[+] Feedback